#### Master project, 2025-2026

# Power Converter Topology and PWM Method Influence on EMI Filter Design

Supervisor : Arnaud VIDET, L2EP – Univ. Lille Email: arnaud.videt@univ-lille.fr

# Context

Electrical energy is managed by power electronics converters in a huge amount of applications from daily-life home appliances to high-power industrial systems. Among them, photovoltaics (PV) make use of DC/DC converters for maximum power point tracking and DC/AC inverters for grid connection, where different converter topologies and pulse-width modulation (PWM) methods may be employed. Because of high commutation frequency and fast switching transients, such converters produce high-frequency (HF) electromagnetic interferences (EMI) that require bulky and costly filters to ensure compliance with applicable electromagnetic compatibility (EMC) standards.

While EMI can be reduced at source by means of multilevel converter topologies and dedicated control methods [1–2], the practical impact of such techniques on actual filter design is not sufficiently worked out. Likewise, state-of-the art EMI filter design methods lack comprehensive analysis of key topology and control parameters as input variables, which constitute a research gap to be addressed in this project.

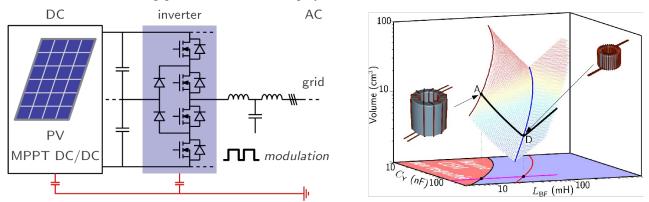

Figure 1: (left) PV and grid-connected multilevel inverter; (right) EMI filter volume optimisation

### **Objectives**

The Power Electronics team of the L2EP laboratory has extensive expertise in energy-efficient and EMI-friendly modulation methods for conventional and multilevel converters [3], and developed advanced EMI filter design methods to optimize filter size in power conversion systems [4] (Figure 1), improving the power density, cost, and environmental footprint of the converter. Based on this know-how, the objective of this research is to link both aspects by 1) analysing the influence of converter topology and PWM control method on optimal filter design, and 2) providing design rules to determine the best topology and control strategy depending on the application requirements. Both 2-level and 3-level inverters will be considered, and quantitative analysis of expected volume gains is expected in the end.

### **Schedule**

Motivated candidates should apply at the above email address to request an appointment, providing latest transcripts. If the application is selected as part of the master thesis program, then preliminary works will be proposed in the first few months to gradually acquire specific knowledge on the subject. It includes a bibliographic study focusing on EMC notably in PV systems, and an intermediate scientific project related to circuit simulations of EMI-reducing PWM methods. Thus, the full-time internship in the second semester will take benefit from the former projects and continue toward the aforementioned objectives. The work will take place in the ESPRIT building of the University of Lille.

# References

- [1] Z. Yang et al. "A Carrier-Based Discontinuous PWM for an 80 kW PV Inverter With the Reduction of the DC-Link Voltage Ripple and Common Mode Current," in IEEE Trans. on Industrial Electronics, vol. 70, no. 7, pp. 6953-6963, July 2023. https://doi.org/10.1109/TIE.2022.3199936

- [2] H. Cheng et al., "A Modified Carrier-Based PWM Strategy for Common Mode Voltage Elimination and Neutral Point Voltage Balance in a Unidirectional Three-Level Converter for AC Motor Drives," in IEEE Trans. on Industrial Electronics, vol. 71, no. 10, pp. 11876-11887, Oct. 2024. https://doi.org/10.1109/TIE.2024.3349568

- [3] A. Videt et al., "PWM Strategy for the Cancellation of Common-Mode Voltage Generated by Three-Phase Back-to-Back Inverters," in IEEE Trans. on Power Electronics, vol. 32, no. 4, pp. 2675-2686, April 2017. https://doi.org/10.1109/TPEL.2016.2573831

- [4] B. Zaidi et al., "Optimization Imethod of CM Inductor Volume Taking Into Account the Magnetic Core Saturation Issues," in IEEE Trans. on Power Electronics, vol. 34, no. 5, pp. 4279-4291, May 2019. https://doi.org/10.1109/TPEL.2018.2861620