École doctorale régionale Sciences Pour l'Ingénieur Lille Nord-de-France

Laboratoire d'Electrotechnique et d'Electronique de puissance (L2EP)

Institut d'Electronique, de Microélectronique et de Nanotechnologies (IEMN)

# Caractérisation et Modélisation de Composants GaN pour la Conception de Convertisseurs Statiques Haute Fréquence

Thèse présentée en vue d'obtenir le grade de Docteur en Génie Electrique par

### Loris Pace

Présentée et soutenue publiquement le 25 novembre 2019 devant le jury :

M. Zoubir KHATIR, Directeur de Recherche à l'IFSTTAR, Président du jury Mme. Nathalie BATUT, Maitre de Conférences HDR à l'Université de Tours, Rapporteur M. Jean-Christophe NALLATAMBY, Professeur à l'Université de Limoges, Rapporteur Mme. Marina DENG, Maitre de Conférences à l'Université de Bordeaux, Examinatrice

- M. Nadir IDIR, Professeur à l'Université de Lille, Directeur de thèse

- M. Jean-Claude DE JAEGER, Professeur à l'Université de Lille, Co-directeur de thèse

- M. Nicolas DEFRANCE, Maitre de Conférences à l'Université de Lille, Co-encadrant

- M. Arnaud VIDET, Maitre de Conférences à l'Université de Lille, Co-encadrant

- M. Ke LI, Chercheur à l'Université de Nottingham (GB), Invité

## Remerciements

Ces travaux de thèse ont été effectués au sein du Laboratoire d'Electrotechnique et d'Electronique de Puissance (L2EP), dirigé par le Professeur Betty Lemaire-Semail, dans l'équipe Electronique de Puissance, dirigée par le Professeur Philippe Lemoigne ainsi qu'au sein de l'Institut d'Electronique, de Microélectronique et de Nanotechnologies (IEMN), dirigé par M. Lionel Buchaillot, dans l'équipe Puissance, dirigée par le Professeur Jean-Claude De Jaeger. Je remercie l'ensemble de ces personnes de m'avoir accueilli au sein de ces deux laboratoires de recherche.

J'adresse mes sincères remerciements à M. Zoubir Khatir, directeur de recherche à l'IFSTTAR, qui m'a fait l'honneur de présider mon jury de thèse. Ces remerciements s'adressent également à Mme Nathalie Batut, Maitre de Conférences HDR au laboratoire Greman de Tours et M. Jean-Christophe Nallatamby, Professeur au laboratoire XLIM de Limoges, pour avoir accepté de juger ce travail en qualité de rapporteurs. Je remercie également Mme Marina Deng, Maitre de Conférences au laboratoire IMS de Bordeaux d'avoir accepté de participer à ce jury en qualité d'examinatrice ainsi que M. Ke Li, chercheur au laboratoire PEMC de Nottingham, de m'avoir fait l'honneur de participer à cette commission d'examen.

J'adresse ma plus profonde gratitude à mon directeur de thèse, le Professeur Nadir Idir ainsi qu'à mon co-directeur de thèse, le Professeur Jean-Claude De Jaeger pour m'avoir fait confiance pour traiter de ce sujet et m'avoir permis d'intégrer deux laboratoires de recherche, le L2EP et l'IEMN, aux savoir-faire complémentaires. Je les remercie vivement pour leur disponibilité tout au long de la thèse, l'expérience qu'ils ont su me faire partager ainsi que leurs apports scientifiques et leur sens pédagogique. Je remercie profondément mes encadrants de thèse, M. Nicolas Defrance et M. Arnaud Videt, Maitres de Conférences à l'université de Lille, pour leur disponibilité, leurs qualités scientifiques et humaines, leurs conseils et leur soutien tout au long de ces trois années. Les personnalités toutes différentes de cette équipe d'encadrants ont généré autant de modèles pour moi et mon futur.

Un grand merci au support technique des deux laboratoires, Mme Vanessa Avramovic et Messieurs Thierry Duquesne, Etienne Okada et Olivier Ferla pour leur aide essentielle au cours de ces travaux. Cette thèse, principalement expérimentale, n'aurait pu être menée sans leur contribution.

Je remercie la direction de l'école Polytech Lille de m'avoir permis de dispenser des enseignements en qualité de docteur assistant au cours de cette thèse. Je remercie également les membres du laboratoire L2EP Messieurs Florian Chevalier, Abdelkader Benabou, Philippe Delarue et Reda Bakri qui font ou qui ont fait partie de l'équipe pédagogique à laquelle j'ai été rattaché et avec qui j'ai pu travailler.

Je souhaite remercier l'ensemble des membres, permanents et non permanents, des deux laboratoires L2EP et IEMN que j'ai eu la chance de rencontrer durant ces trois ans. Tous ces êtres exceptionnels se reconnaitront certainement. Je remercie particulièrement les membres de l'équipe Electronique de Puissance au L2EP et de l'équipe Puissance à l'IEMN que j'ai pu côtoyer au quotidien : Bilel, Ammar, Stéphane, Florentin, Hugot, Wendell, Caroline, Walid, Hadrien, Mahmoud, Rheda, Issa, Maxime...

Enfin, je remercie de tout cœur les membres de ma famille qui m'ont soutenu. Notamment mes parents qui m'ont toujours fait confiance dans mes choix de vie.

## Résumé

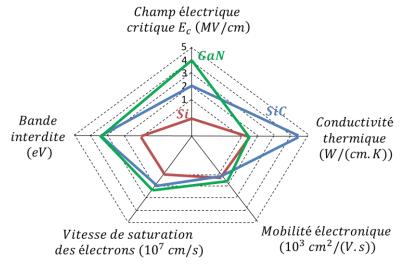

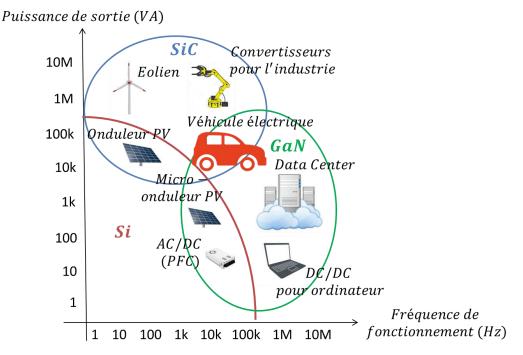

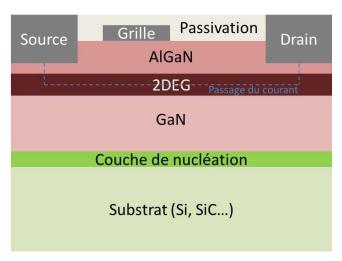

La montée en fréquence de commutation des transistors de puissance à base de Nitrure de Gallium (GaN) présente une avancée technologique conduisant à la réduction de la taille, du poids et du volume des systèmes de conversion de l'énergie. En effet, les propriétés physiques des transistors de type HEMT basés sur l'hétérostructure AlGaN/GaN présentent un fort potentiel pour le développement de convertisseurs statiques haute fréquence. Avec l'augmentation toujours croissante de la part de l'électronique de puissance dans les systèmes électriques actuels, cette filière technologique, associée à la filière du Carbure de Silicium (SiC), vise aujourd'hui à remplacer progressivement les composants de puissance à base de Silicium (Si) notamment pour des raisons de tension de claquage élevée, de robustesse vis-à-vis des conditions sévères de fonctionnement et d'intégration de puissance.

La conception optimale des convertisseurs haute fréquence implique une connaissance précise du fonctionnement des composants de puissance au sein de ces systèmes. Ainsi, la conception de ces dispositifs repose sur des étapes d'analyse et de simulations menées à partir des modèles des semi-conducteurs de puissance et des éléments environnants. L'objectif de ce travail de thèse est de proposer une méthodologie de modélisation comportementale de transistors de puissance GaN en boitier basée exclusivement sur des méthodes de caractérisation non-intrusives.

Les techniques de caractérisation électriques utilisées pour la modélisation de transistors fonctionnant en gammes radiofréquences, telles que la mesure des paramètres S ou les mesures courant/tension en régime pulsé, sont ici adaptées à la caractérisation du transistor de puissance GaN encapsulé. A partir des résultats de caractérisation, les différents éléments linéaires et non linéaires du modèle électrique du transistor sont obtenus et un modèle électrique complet rassemblant ces éléments est implémenté dans le logiciel de simulation ADS. Un banc de test Double Pulse est alors conçu afin de mettre en application le modèle électrique développé. Après modélisation de l'environnement du transistor, y compris du circuit imprimé, les résultats de simulation des formes d'onde de commutation sont confrontés aux résultats expérimentaux.

Afin de tenir compte des effets de la température sur le fonctionnement du transistor, une méthodologie est proposée permettant d'obtenir le modèle thermique du composant à partir de mesures de puissance dissipée et d'une procédure d'optimisation. À partir du modèle obtenu, un convertisseur DC/DC utilisant le transistor GaN modélisé a été conçu et réalisé. Les résultats de simulation des formes d'onde de commutation sont confrontés aux résultats expérimentaux pour différentes températures de fonctionnement du transistor et une prédiction du fonctionnement en continu du convertisseur est réalisée.

## **Abstract**

The high frequency operation of GaN power transistors is of great interest in order to reduce size, weight and volume of power converters. Indeed, GaN HEMT power transistors show very good physical properties for the development of high frequency power converters. Within the constant rise of the amount of power electronics in electrical systems, the GaN technology, associated with the Silicon Carbide (SiC) one, aims to progressively replace the Silicium (Si) power devices especially in terms of robustness in harsh conditions and of power integration.

The optimal design of high frequency power converters involves an accurate knowledge of power devices operations in the systems. Therefore, before the fabrication of converters, simulations steps based on semi-conductor and surrounding elements models are required. This research work focuses on the development of a modeling methodology of packaged GaN power transistors, exclusively based on non-intrusive characterization techniques.

In this work, electrical characterization techniques used for radiofrequency transistors modeling, such as S-parameters and pulsed current/voltage measurements, are adapted to characterize the packaged GaN power transistor. Based on the characterization results, linear and nonlinear elements of the transistor's electrical equivalent circuit are determined and a complete electrical model of the device is implemented in the ADS software. A Double Pulse test bench is made in order to apply the developed electrical model. After having modeled the whole test bench, including the printed circuit board, simulation results of the switching waveforms are compared to experimental results.

Considering the effects of transistor's temperature on its operation in power converters, a methodology is proposed to extract the thermal model of the device using dissipated power measurements and an optimization procedure. The obtained thermal circuit and its influence of thermal-dependent elements are added to the previous electrical model in order to build the complete electro-thermal model of the GaN power transistor. Based on the developed model, a DC to DC converter using the studied transistor has been designed and fabricated. Then, the simulation results are compared to experimental results for several operating temperatures and a prediction of the continuous operation of the converter is achieved.

# Table des matières

| Remerciemen      | ts                                                                                                                              | i    |

|------------------|---------------------------------------------------------------------------------------------------------------------------------|------|

| Résumé           |                                                                                                                                 | ii   |

| Abstract         |                                                                                                                                 | iii  |

| Liste des figur  | es                                                                                                                              | vii  |

| Liste des table  | eaux                                                                                                                            | xiii |

| Glossaire        |                                                                                                                                 | xiv  |

| Introduction g   | généralegénérale                                                                                                                | 1    |

| -                | troduction à la modélisation de transistors de puissance GaN pour la conception de s statiques fonctionnant à hautes fréquences |      |

| Introductio      | n                                                                                                                               | 4    |

| I.1. Les         | composants semi-conducteurs pour la conversion d'énergie à hautes fréquences                                                    | 5    |

| I.1.1.           | Présentation de composants semi-conducteurs en électronique de puissance                                                        | 5    |

| I.1.1.1          | . Contexte                                                                                                                      | 5    |

| I.1.1.2          | . La diode de puissance                                                                                                         | 6    |

| I.1.1.3          | . Le transistor de puissance à effet de champ                                                                                   | 8    |

| 1.1.2.           | La cellule de commutation                                                                                                       | 10   |

| I.1.3.           | Montée en fréquence des convertisseurs                                                                                          | 13   |

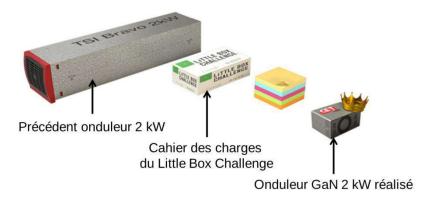

| 1.1.4.           | Convertisseurs à haute densité de puissance                                                                                     | 14   |

| I.2. Les         | transistors de puissance GaN                                                                                                    | 15   |

| I.2.1.           | Intérêt du nitrure de gallium pour l'électronique de puissance hautes fréquences                                                | 15   |

| 1.2.2.           | Technologies et propriétés des transistors de puissance GaN                                                                     | 17   |

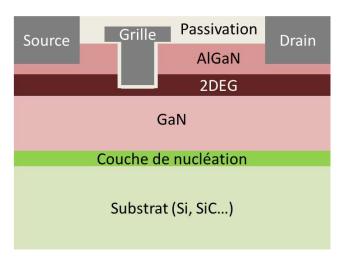

| 1.2.2.1          | . La structure GaN HEMT                                                                                                         | 17   |

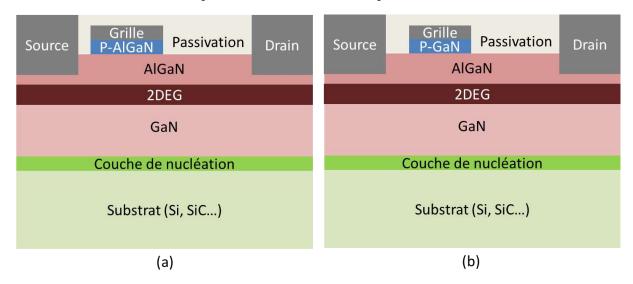

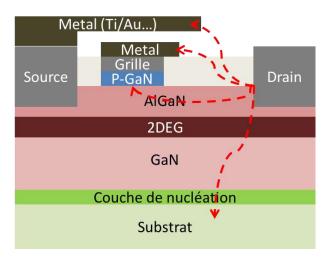

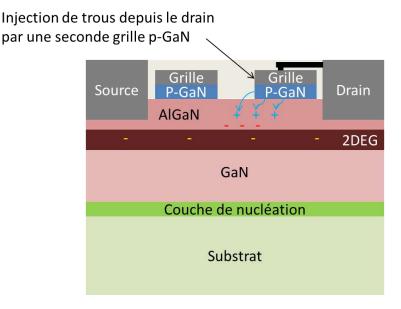

| 1.2.2.2          | . Technologies des transistors GaN « normally-off»                                                                              | 19   |

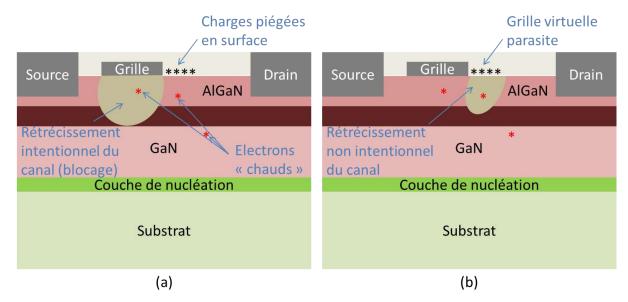

| 1.2.2.3          | . Phénomène de résistance dynamique dans les transistors GaN HEMT                                                               | 21   |

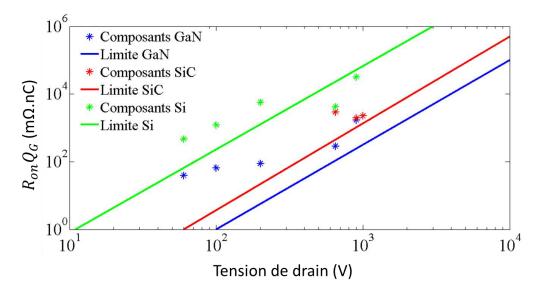

| 1.2.3.           | Etat de l'art des transistors de puissance GaN                                                                                  | 23   |

| I.3. Mod         | délisation des transistors de puissance GaN                                                                                     | 25   |

| I.3.1.           | Intérêt de la modélisation des transistors de puissance GaN                                                                     | 25   |

| 1.3.2.           | Modélisation physique                                                                                                           | 26   |

| 1.3.3.           | Modélisation comportementale                                                                                                    | 26   |

| Conclusion       |                                                                                                                                 | 28   |

| Bibliograph      | ie du chapitre I                                                                                                                | 29   |

| Chapitre II : Ca | aractérisation en paramètres S d'un transistor de puissance GaN en boitier                                                      | 33   |

| Introductio      | n                                                                                                                               | 33   |

| II.1.<br>S | Techniques de caractérisation du transistor de puissance GaN par la mesure de par<br>34 | ramètres  |

|------------|-----------------------------------------------------------------------------------------|-----------|

| II.1       | L.1. La mesure des paramètres S                                                         | 34        |

| II.1       | L.2. Caractérisation en paramètres S des transistors GaN                                | 35        |

| II.1       | 3. Dispositifs de caractérisation en paramètres S d'un transistor de puissance GaN e    | n boitier |

|            |                                                                                         | 37        |

| II.1       | 4. Caractérisation en paramètres S sous des polarisations jusqu'à 400 V et 10 A         | 46        |

| II.2.      | Détermination des éléments d'accès du transistor GaN                                    | 50        |

| 11.2       | 2.1. Détermination des éléments d'accès du transistor GS66502B                          | 51        |

| 11.2       | 2.2. Détermination des éléments d'accès d'un transistor GaN avec source Kelvin          | 59        |

| 11.2       | 2.3. Dépendance en température des résistances d'accès                                  | 62        |

| II.3.      | Caractérisation des capacités inter-électrodes                                          | 64        |

| 11.3       | $8.1.$ Mesure des capacités inter-électrodes en fonction de $	extbf{\emph{VDS}}$        | 64        |

| 11.3       | 3.2. Mesure des capacités inter-électrodes en fonction de $\it VGS$                     | 66        |

| Conc       | lusion                                                                                  | 67        |

| Biblio     | ographie du chapitre II                                                                 | 68        |

| Chapitr    | e III : Modélisation électrothermique d'un transistor de puissance GaN en boitier       | 71        |

| Intro      | duction                                                                                 | 71        |

| III.1.     | Modélisation électrique du transistor GaN                                               | 72        |

| III.       | 1.1. Modélisation des capacités inter-électrodes                                        | 72        |

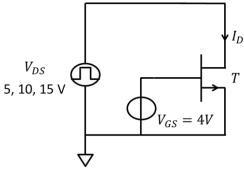

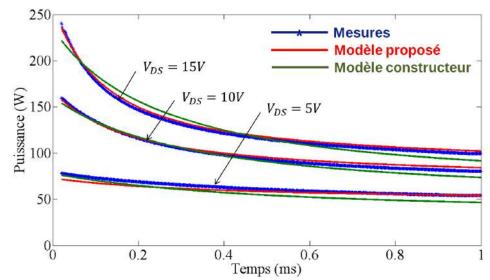

| III.       | 1.2. Modélisation des sources de courant                                                | 75        |

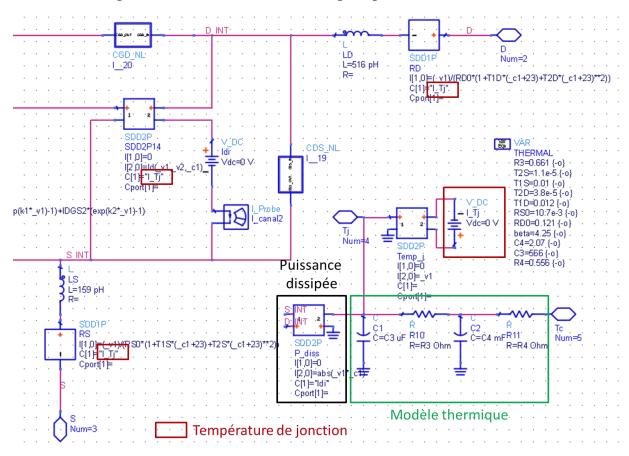

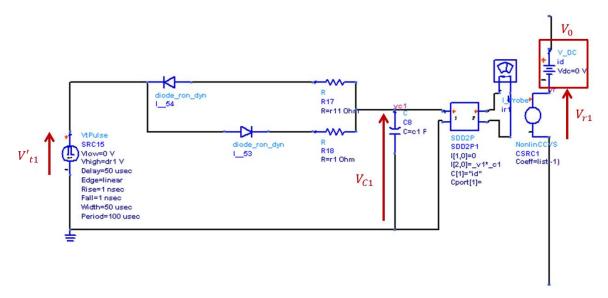

| III.       | 1.3. Implémentation du modèle électrique du transistor GaN sous ADS                     | 81        |

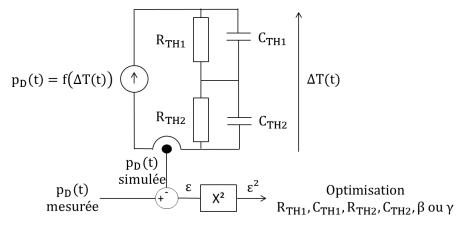

| III.2.     | Modélisation thermique du transistor GaN                                                | 85        |

| III.       | 2.1. Mesures de puissance dissipée en régime pulsé                                      | 85        |

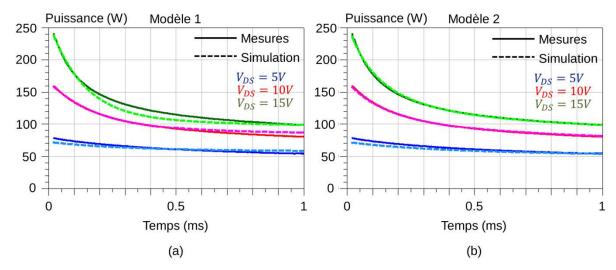

| III.       | 2.2. Modélisation thermique                                                             | 87        |

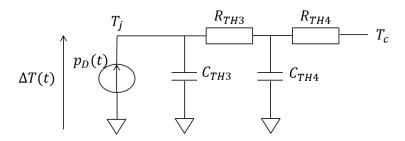

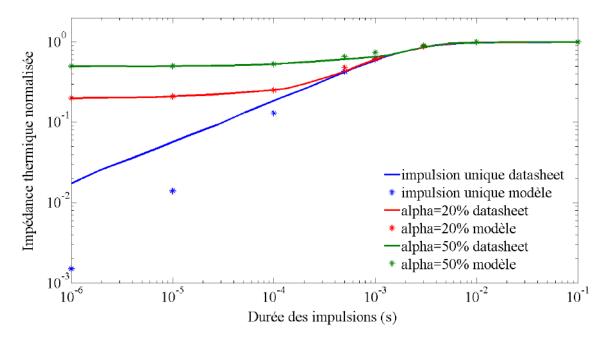

| III.       | 2.3. Implémentation du modèle thermique                                                 | 92        |

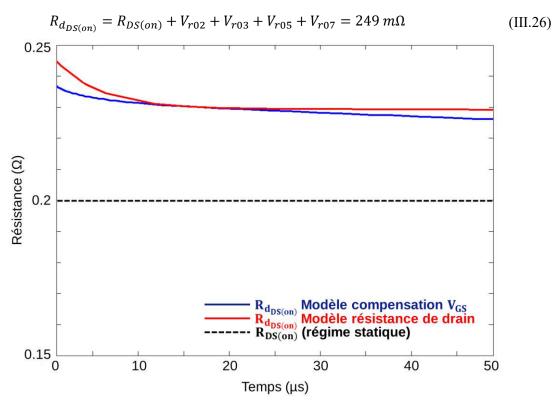

| III.3.     | Modélisation du phénomène de résistance dynamique                                       | 93        |

| III.       | 3.1. Modélisation par compensation de la tension grille-source                          | 93        |

| III.       | 3.2. Modélisation par la résistance de drain                                            | 96        |

| III.       | 3.3. Comparaison des modèles de la résistance dynamique                                 | 98        |

| Conc       | lusion                                                                                  | 100       |

| Biblio     | ographie du chapitre III                                                                | 101       |

|            | e IV : Utilisation des modèles de composants de puissance pour la conception de         |           |

|            | isseurs statiques haute fréquence                                                       | 103       |

| Intro      | duction                                                                                 | 103       |

| IV.1.      | Validation du modèle électrique du transistor de puissance GaN                          | 104       |

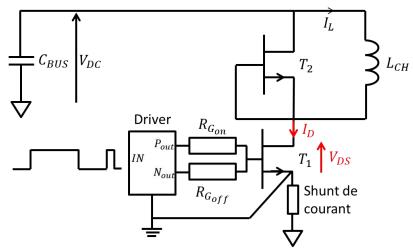

| IV         | 1.1. Concention du circuit Double Pulse                                                 | 104       |

|     | IV.1.2    | Modélisation du circuit Double Pulse                            | 107 |

|-----|-----------|-----------------------------------------------------------------|-----|

|     | IV.1.3    | Analyse des performances du modèle électrique du transistor GaN | 112 |

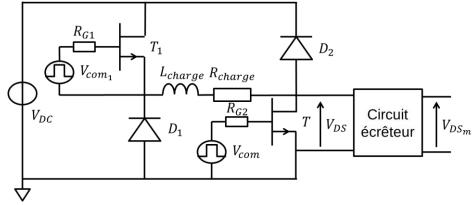

|     | IV.2.     | Conception et modélisation d'un convertisseur DC/DC à 1 MHz     | 114 |

|     | IV.2.1    | Structure du convertisseur                                      | 114 |

|     | IV.2.2    | Conception et modélisation de la maille de grille               | 115 |

|     | IV.2.3    | Choix de la diode SiC                                           | 116 |

|     | IV.2.4    | Conception et modélisation du circuit de refroidissement        | 124 |

|     | IV.3.     | Validation du modèle électrothermique du transistor GaN         | 127 |

|     | IV.3.1    | Test en Double Pulse sur le convertisseur GaN/SiC               | 127 |

|     | IV.3.2    | Tests en Double Pulse à différentes températures de jonction    | 129 |

|     | IV.3.3    | Fonctionnement répétitif du convertisseur GaN/SiC               | 133 |

|     | Conclusi  | on                                                              | 136 |

|     | Bibliogra | phie du chapitre IV                                             | 137 |

| Cc  | onclusion | générale                                                        | 138 |

| _is | ste des p | ublications                                                     | 141 |

# Liste des figures

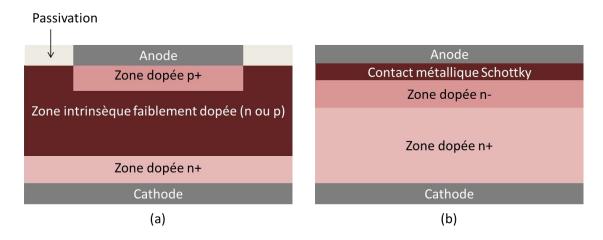

| Figure I. 1 : Structures de base des diodes utilisées en électronique de puissance : (a) Diode PiN      |        |

|---------------------------------------------------------------------------------------------------------|--------|

| (b) Diode Schottky                                                                                      | 6      |

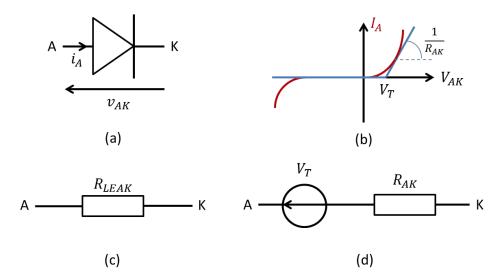

| Figure I. 2 : (a) caractéristique statique d'une diode (b) schéma équivalent statique de la diode pou   | ır     |

| VAK < VT (c) schéma équivalent statique de la diode pour VAK > VT                                       | 7      |

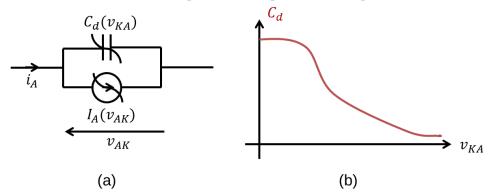

| Figure I. 3 : (a) Modèle intrinsèque non linéaire de la diode de puissance (b) Evolution de la capac    | ité    |

| Cd en fonction de la tension inverse aux bornes de la diode vKA                                         | 7      |

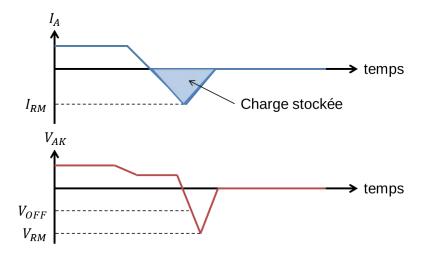

| Figure I. 4 : Phénomène de recouvrement inverse de la diode au blocage                                  | 8      |

| Figure I. 5 : Présentation du transistor de puissance à effet de champ : (a) Symbole électrique et      |        |

| conventions (b) structure horizontale (exemple : JFET (Junction Field Effect Transistor)) (c) Structure | cture  |

| verticale (exemple : MOSFET)                                                                            | 8      |

| Figure I. 6 : Exemple de caractéristique statique d'un transistor à effet de champ                      | 9      |

| Figure I. 7 : Modèle électrique non linéaire de la partie intrinsèque d'un transistor de puissance      | 9      |

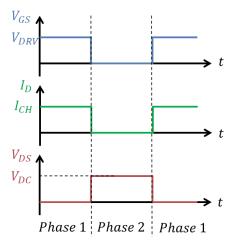

| Figure I. 8: (a) structure du convertisseur Buck (b) phases de fonctionnement du convertisseur          | 10     |

| Figure I. 9 : Allure des formes d'onde idéales sur une phase de fonctionnement du convertisseur         | 10     |

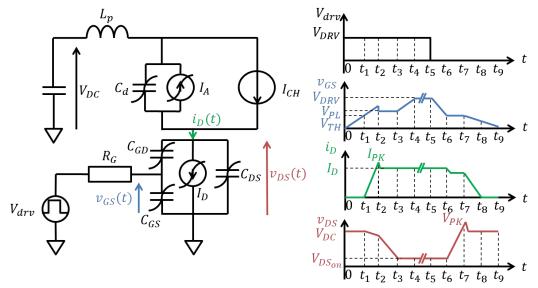

| Figure I. 10 : (a) Schéma du convertisseur avec modèles des semi-conducteurs de puissance (b) Fo        | ormes  |

| d'ondes simplifiées à la mise en conduction et au blocage du transistor                                 | 11     |

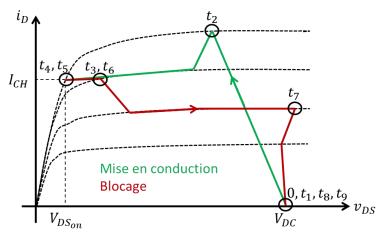

| Figure I. 11 : Trajectoires simplifiées des commutations dans le plan $iD(vDS)$                         | 12     |

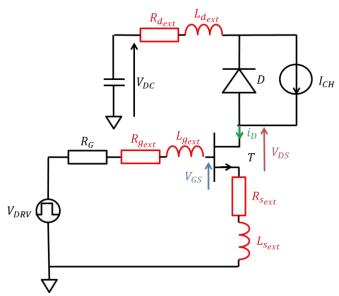

| Figure I. 12 : Identification des éléments parasites du convertisseur influant sur les formes d'ond     | le des |

| commutations du transistor                                                                              | 12     |

| Figure I. 13 : Convertisseur GaN 2 kW réalisé par les vainqueurs du Little Box Challenge (Source        | :      |

| [I.17])                                                                                                 | 14     |

| Figure I. 14 : Comparaison des propriétés physiques des matériaux Si, SiC et GaN pour des               |        |

| applications d'électronique de puissance [I.24]                                                         |        |

| Figure I. 15 : Domaines d'application des différents semi-conducteurs de l'électronique de puissar      |        |

| base de Si, SiC et GaN [I.25]                                                                           |        |

| Figure I. 16 : Structure de base d'un transistor GaN HEMT                                               |        |

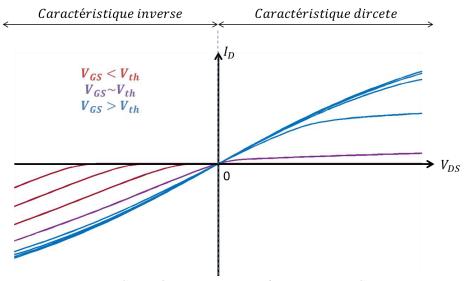

| Figure I. 17 : Caractéristique statique d'un transistor GaN HEMT                                        |        |

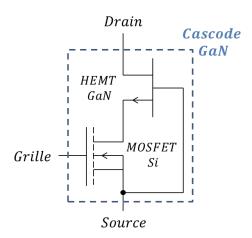

| Figure I. 18: Structure d'un transistor de puissance GaN en montage cascode                             |        |

| Figure I. 19: Technique de « recess » de grille sur un transistor GaN HEMT                              |        |

| Figure I. 20: Structures des transistors GaN: (a) GIT (b) HEMT P-GaN                                    |        |

| Figure I. 21 : Mécanismes de piégeages à l'origine du phénomène de résistance dynamique dans le         |        |

| HEMT GaN: (a) lors de l'état bloqué du composant (b) lors de la mise en conduction                      |        |

| Figure I. 22 : Répartition du champ électrique par utilisation du substrat et de répartisseurs métalli  | •      |

| au niveau de la grille et de la source                                                                  |        |

| Figure I. 23 : Relâchement des électrons piégés par injection de trous en implémentant d'une secon      |        |

| grille p-GaN (structure HD-GIT)                                                                         |        |

| Figure I. 24 : Figures de mérite pour différents transistors de puissance GaN, SiC et Si en fonction    |        |

| calibres en tension [I.44]                                                                              |        |

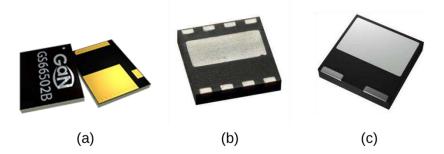

| Figure I. 25 : Exemples de transistors de puissance GaN 600/650 V : (a) GS66502B de GaN Syste           |        |

| (b) PGA26E19BA de Panasonic (c) TP65H300G4LSG de Transphorm                                             |        |

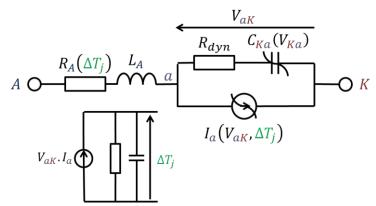

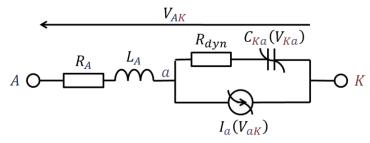

| Figure I. 26 : modèle électrothermique d'une diode de puissance                                         |        |

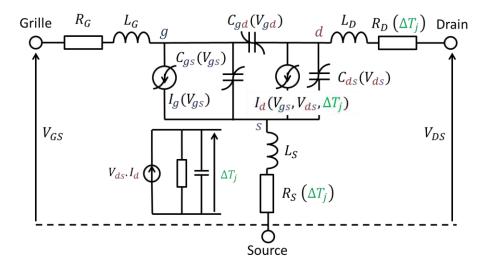

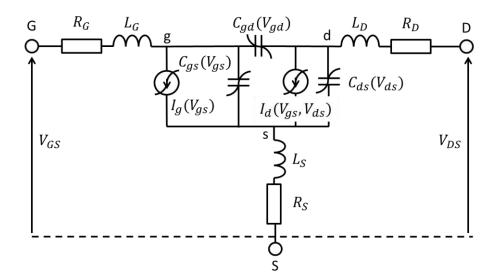

| Figure I. 27 : modèle électrothermique d'un transistor de puissance à effet de champ                    | 27     |

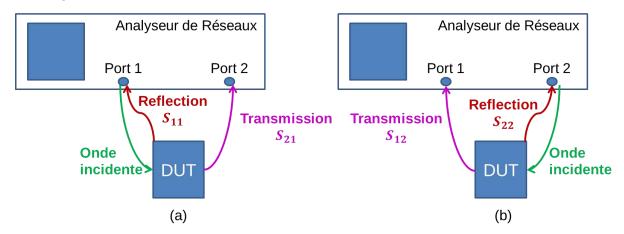

| Figure II. 1 : Principe d'une mesure de paramètres S en 2 ports : (a) injection du signal sur le port 1         | (b)  |

|-----------------------------------------------------------------------------------------------------------------|------|

| injection du signal sur le port 2                                                                               | 34   |

| Figure II. 2 : Schéma de principe d'une caractérisation en paramètres S d'un transistor                         | 35   |

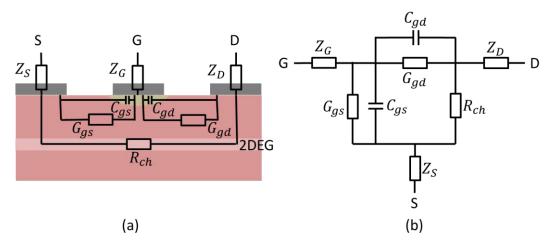

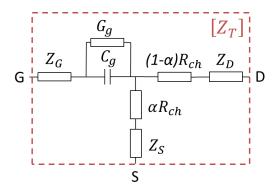

| Figure II. 3 : Schéma équivalent petit signal d'un transistor GaN HEMT [II.14]                                  | 36   |

| Figure II. 4 : Représentation de la partie intrinsèque du transistor sous la forme d'un quadripôle              | 37   |

| Figure II. 5 : (a) présentation du transistor GaN GS66502B (b) comparaison de boitiers GaN-PX vs                |      |

| TO-220 [II.15]                                                                                                  | 38   |

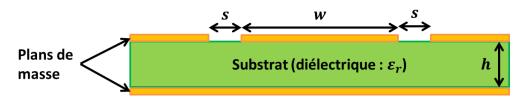

| Figure II. 6 : Ligne de transmission avec plans de masse coplanaires et inférieurs                              | 39   |

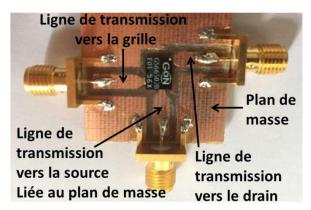

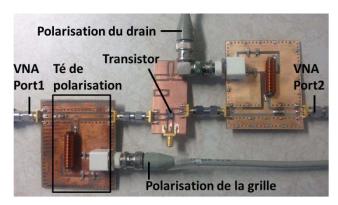

| Figure II. 7 : Système de caractérisation 2 ports en paramètres S du transistor GS66502B                        | 40   |

| Figure II. 8 : Schéma équivalent du dispositif de caractérisation du transistor de la figure II.7               |      |

| Figure II. 9 : Standards de calibration et schémas équivalents associés : (a) OPEN1P (b) SHORT (c)              | )    |

| OPEN2P                                                                                                          | 41   |

| Figure II. 10 : Modélisation du PCB comportant les standards de calibration sur ADS : (a) définition            | ı du |

| substrat (b) vue 3D du PCB importé                                                                              |      |

| Figure II. 11 : Schéma de simulation ADS d'une mesure de paramètres S sur le standard OPEN1P                    | 43   |

| Figure II. 12 : Comparaison entre résultats de mesure et de simulation sur le standard OPEN1P                   | 44   |

| Figure II. 13 : Schéma de simulation ADS d'une mesure de paramètres S sur le standard SHORT                     | 44   |

| Figure II. 14 : Comparaison entre résultats de mesure et de simulation sur le standard SHORT                    |      |

| Figure II. 15 : Schéma de simulation ADS d'une mesure de paramètres S sur le standard OPEN2P                    |      |

| Figure II. 16 : Comparaison entre résultats de mesure et de simulation sur le standard OPEN2P                   |      |

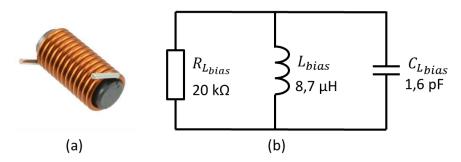

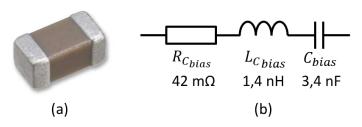

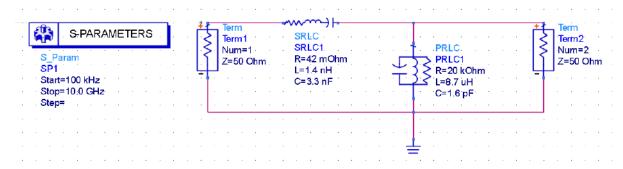

| Figure II. 17 : Schéma interne du Té de polarisation 11612A                                                     |      |

| Figure II. 18 : (a) Présentation de l'inductance du Té de polarisation (b) Modèle électrique de                 |      |

| l'inductance                                                                                                    | 47   |

| Figure II. 19 : (a) Présentation du condensateur du Té de polarisation (b) modèle électrique du                 |      |

| condensateur                                                                                                    | 47   |

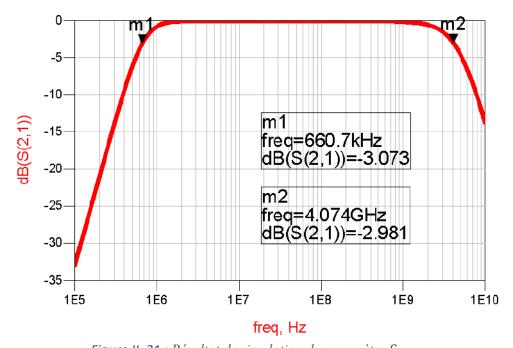

| Figure II. 20 : Schéma de simulation de paramètres S sur le té de polarisation                                  |      |

| Figure II. 21 : Résultat de simulation du paramètre S21                                                         |      |

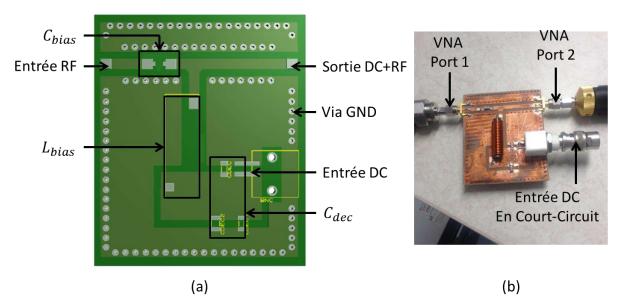

| Figure II. 22 : Té de polarisation sur PCB : (a) conception et disposition des composants (b) mesure            |      |

| paramètres S                                                                                                    |      |

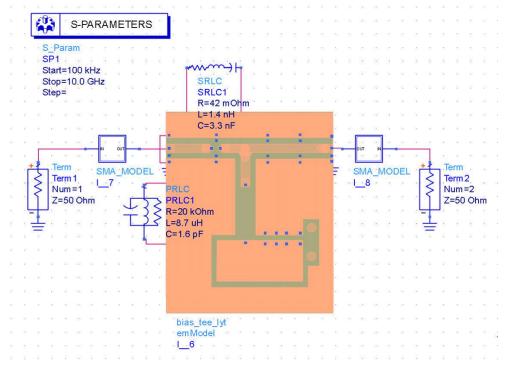

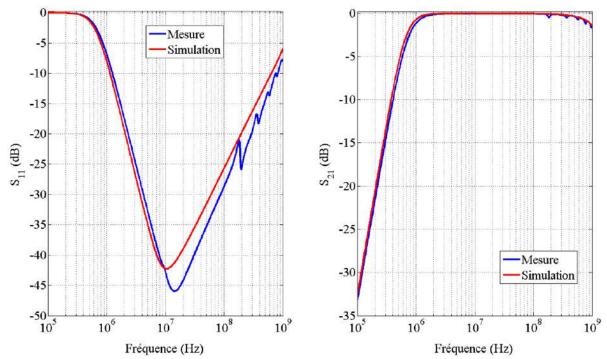

| Figure II. 23 : Schéma de simulation ADS de paramètres S sur le Té de polarisation sur PCB                      |      |

| Figure II. 24 : Paramètres S mesurés et simulés sur le Té de polarisation sur PCB                               |      |

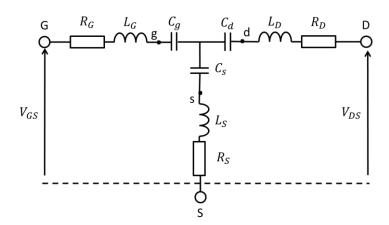

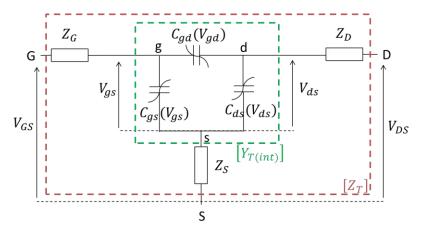

| Figure II. 25 : Modèle électrique du transistor GaN                                                             |      |

| Figure II. 26 : Schéma équivalent du transistor à $VGS = 0V$ et $VDS = 0V$                                      |      |

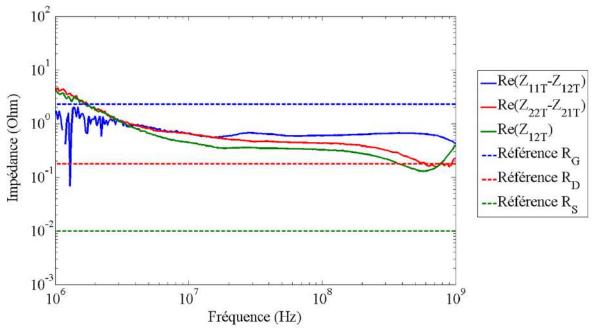

| Figure II. 27: Extraction des résistances d'accès à $VGS = 0V$ et $VDS = 0V$                                    |      |

| Figure II. 28 : Représentation du transistor dans les conditions Cold FET : (a) Coupe schématique               | 55   |

| (b) Circuit électrique équivalent                                                                               | 5/1  |

| Figure II. 29 : Simplification du schéma équivalent du transistor dans les conditions Cold FET                  |      |

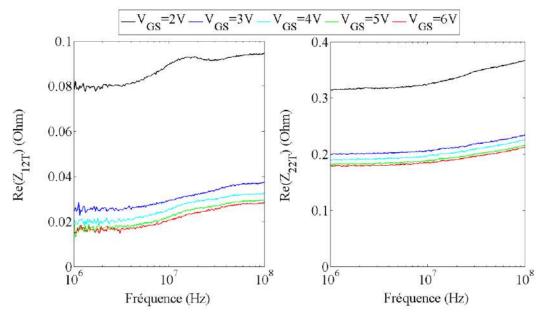

| Figure II. 30 : parties réelles des impédances $Z12T$ et $Z22T$ en fonction de la fréquence pour différe        |      |

| VGS > VTH                                                                                                       |      |

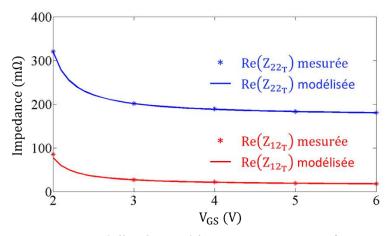

| Figure II. 31 : Parties réelles des impédances Z12T et Z22T en fonction de VGS                                  |      |

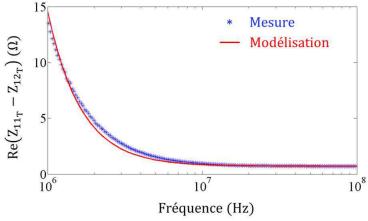

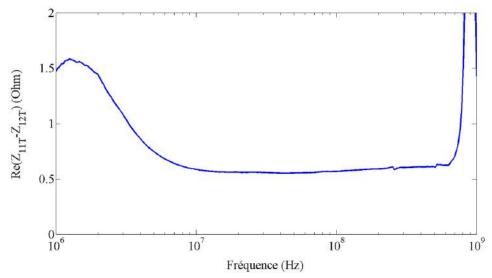

| Figure II. 32 : Partie réelle de l'impédance $Z11T - Z12T$ en fonction de la fréquence pour $VGS = 0$           |      |

| et modélisationet modélisation                                                                                  |      |

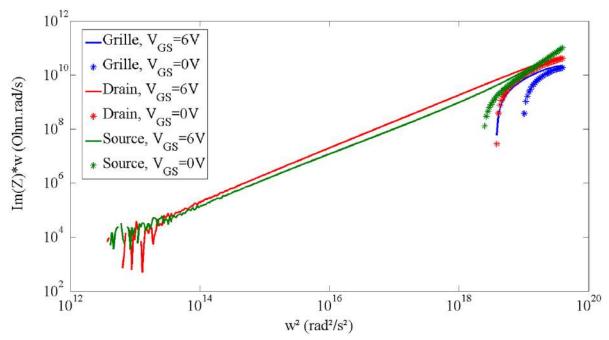

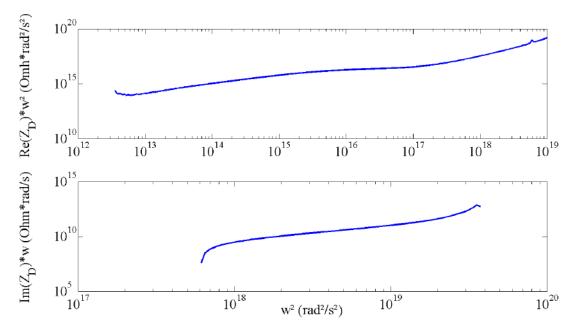

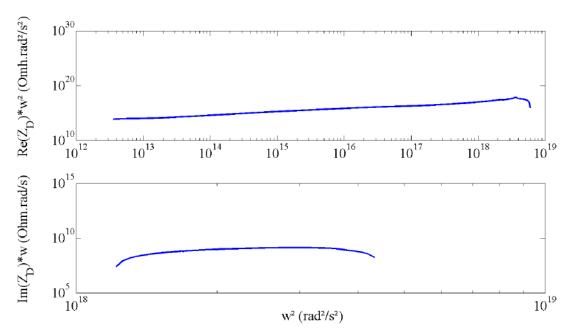

| Figure II. 33 : Évolutions correspondantes aux relations eq.(II.59) à eq.(II.64) en fonction $\omega^2$ pour le |      |

| détermination des résistances d'accès                                                                           |      |

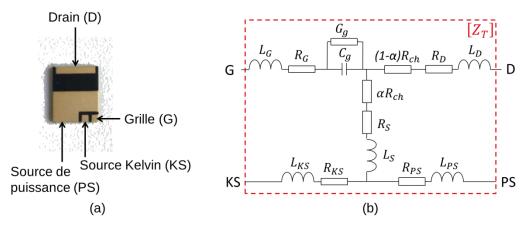

| Figure II. 34 : Présentation du transistor GS66508B (a) Boitier du composant (b) Schéma électrique              |      |

|                                                                                                                 |      |

| équivalent du transistor dans les conditions Cold FET                                                           |      |

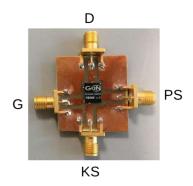

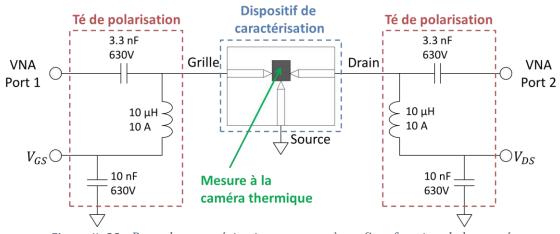

| Figure II. 35: Dispositif de caractérisation du transistor GS66508B                                             |      |

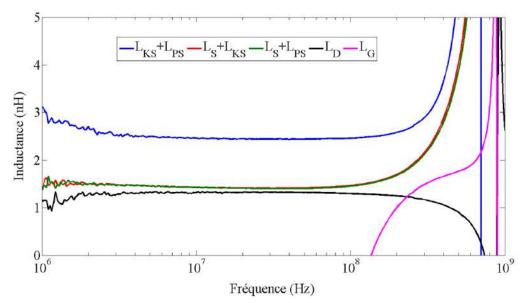

| Figure II. 36: Extraction des inductances d'accès du transistor GS66508B                                        | ხ0   |

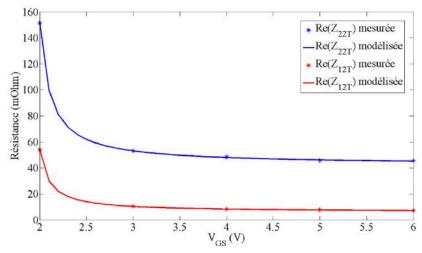

| Figure II. 37 : Extraction des résistances <i>RD</i> et <i>RS</i> + <i>RPS</i> du transistor GS66508B              | 61   |

|--------------------------------------------------------------------------------------------------------------------|------|

| Figure II. 38 : Extraction de la résistance RG du transistor GS66508B                                              | 61   |

| Figure II. 39 : Banc de caractérisation en paramètres S en fonction de la température                              | 62   |

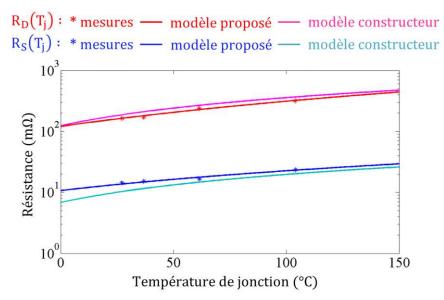

| Figure II. 40 : Comparaison du modèle électrothermique des résistances d'accès proposé avec le modèle constructeur | 64   |

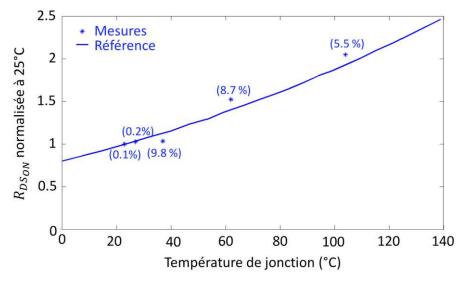

| Figure II. 41 : Comparaison de <i>RDSonTj</i> entre mesures et valeurs de référence de la documentation            |      |

| technique (écarts relatifs entre parenthèses)                                                                      |      |

| Figure II. 42 : Schéma équivalent du transistor à $VGS = 0V$                                                       |      |

| Figure II. 43 : Banc de caractérisation du transistor GaN pour l'extraction des capacités inter-électro            |      |

| rigure ii. 43 . Bane de caracterisation du transistor Gary pour l'extraction des capacites inter-electro           |      |

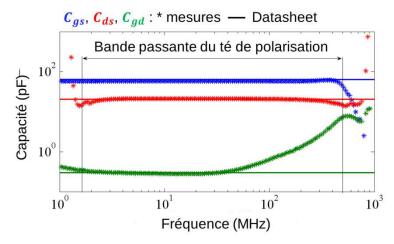

| Figure II. 44 : Extraction des capacités inter-électrodes en fonction de la fréquence à $VDS = 200V$               |      |

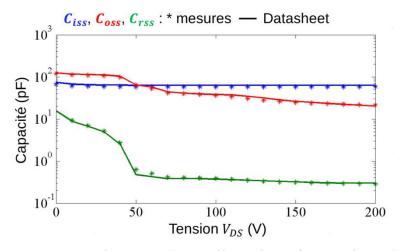

| Figure II. 45 : Extraction des capacités inter-électrodes en fonction de VDS à 10 MHz                              | 66   |

| Figure II. 46 : Schéma équivalent du transistor dans les conditions Cold FET                                       | 67   |

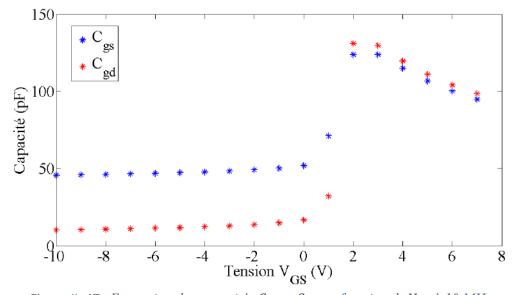

| Figure II. 47 : Extraction des capacités <i>Cgs</i> et <i>Cgd</i> en fonction de <i>VGS</i> à 10 MHz               | 67   |

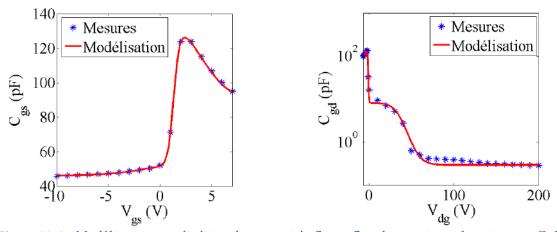

| Figure III. 1 : Modélisation non linéaire des capacités <i>Cgs</i> et <i>Cgd</i> du transistor de puissance GaN    | 73   |

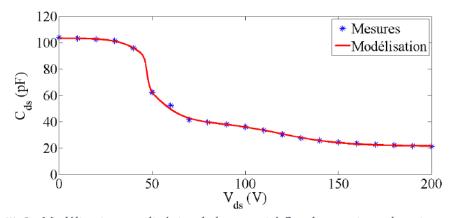

| Figure III. 2 : Modélisation non linéaire de la capacité Cds du transistor de puissance GaN                        | 73   |

| Figure III. 3 : Exemples de modèles SPICE de capacités inter-électrodes pour transistor GaN : (a)                  |      |

| modèle proposé dans [III.4] (b) modèle proposé dans [III.5]                                                        | 74   |

| Figure III. 4 : Modèle non linéaire proposé de capacité inter-électrodes (a) schéma électrique équiva              | lent |

| (b) schéma d'implémentation du modèle sous ADS                                                                     | 75   |

| Figure III. 5 : Schéma de simulation de l'auto-échauffement durant les mesures IV pulsées                          | 76   |

| Figure III. 6 : Simulation de l'auto-échauffement du transistor pour différentes puissances dissipées              |      |

| durant les mesures I-V pulsées                                                                                     | 76   |

| Figure III. 7 : Mesures I-V en régime pulsé sur le transistor de puissance GaN et cartographie de l'au             | uto- |

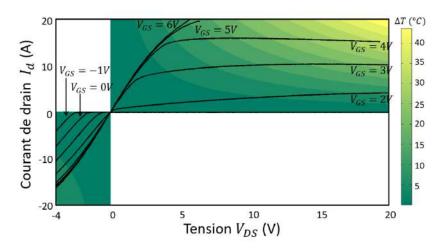

| échauffement du composant                                                                                          | 77   |

| Figure III. 8 : Schéma de la procédure d'optimisation implémentée dans ADS pour déterminer les                     |      |

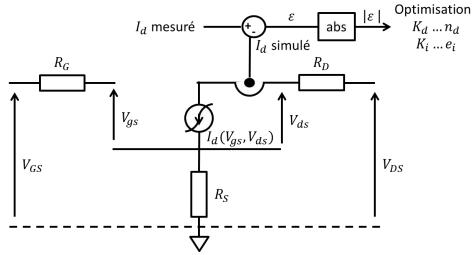

| paramètres du modèle de la source de courant de drain                                                              | 78   |

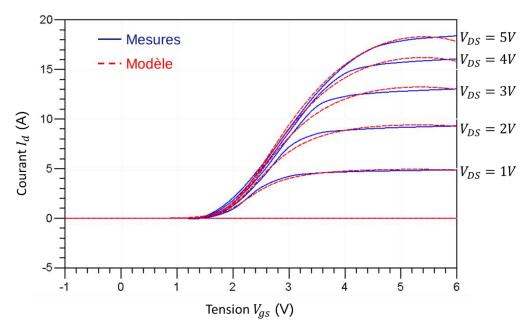

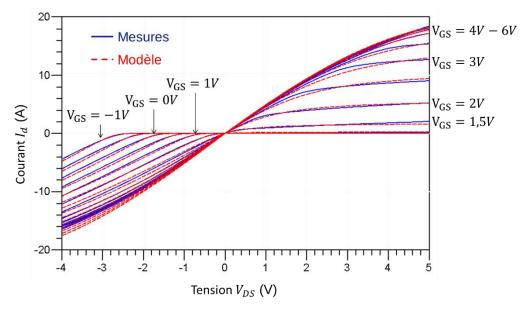

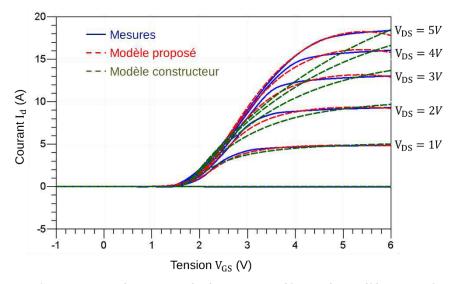

| Figure III. 9 : Mesures et modélisation du courant $Id$ en fonction de la tension $Vgs$                            | 79   |

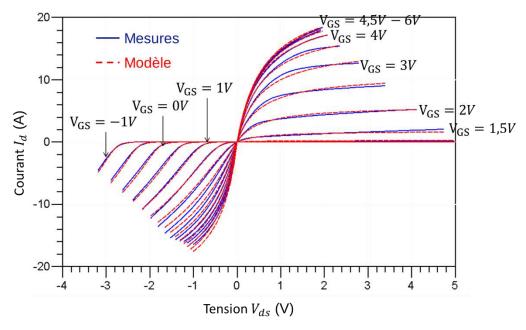

| Figure III. 10 : Mesures et modélisation du courant $Id$ en fonction de la tension $Vds$                           | 79   |

| Figure III. 11: Mesures et modélisation du courant Id en fonction de la tension VDS                                | 80   |

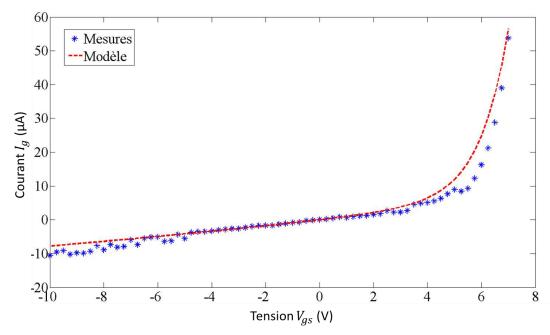

| Figure III. 12 : Mesures et modélisation du courant $Ig$ en fonction de la tension $Vgs$                           | 81   |

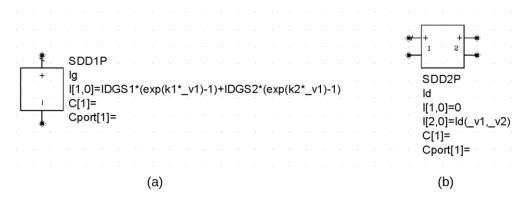

| Figure III. 13 : Modèles des sources de courant : (a) de grille (b) de drain implémentés sous ADS                  | 81   |

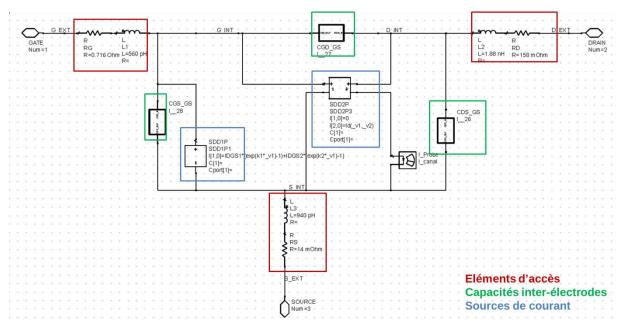

| Figure III. 14 : Modèle électrique du transistor GaN implémenté dans ADS                                           | 82   |

| Figure III. 15 : Schéma de simulation en paramètres S pour la validation de l'implémentation des                   |      |

| capacités inter-électrodes dans le modèle de transistor GaN                                                        | 82   |

| Figure III. 16 : Comparaison des capacités inter-électrodes implémentées dans le modèle proposé et                 |      |

| dans le modèle constructeur en fonction de $VGS$ avec les résultats de mesure à $VDS = 0V$ et à $10~\mathrm{N}$    |      |

|                                                                                                                    |      |

| Figure III. 17 : Comparaison des capacités inter-électrodes implémentées dans le modèle proposé et                 |      |

| dans le modèle constructeur en fonction de $VDS$ avec les résultats de mesure à $VGS = 0V$ et à 10 M               |      |

|                                                                                                                    | 83   |

| Figure III. 18 : Schéma de simulation en paramètres S pour la validation de l'implémentation de la                 | _    |

| source de courant de drain parasites dans le modèle de transistor                                                  | 84   |

| Figure III. 19 : Comparaison du courant de drain <i>Id</i> simulé avec le modèle proposé et le modèle              |      |

| constructeur en fonction de VGS avec les résultats de mesure                                                       | 84   |

| Figure III. 20 : Comparaison du courant de drain <i>Id</i> simulé avec le modèle proposé et le modèle         |        |

|---------------------------------------------------------------------------------------------------------------|--------|

| constructeur en fonction de VDS avec les résultats de mesure                                                  | 85     |

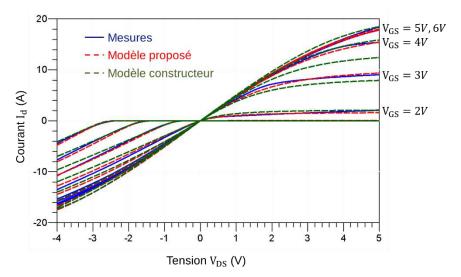

| Figure III. 21 : (a) schéma principe de la mesure de puissances dissipées (b) résultats de mesures d          | e      |

| puissances dissipées sur le transistor GaN                                                                    |        |

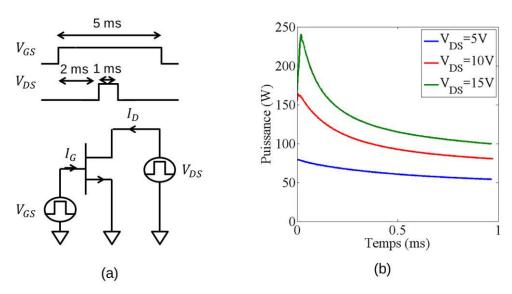

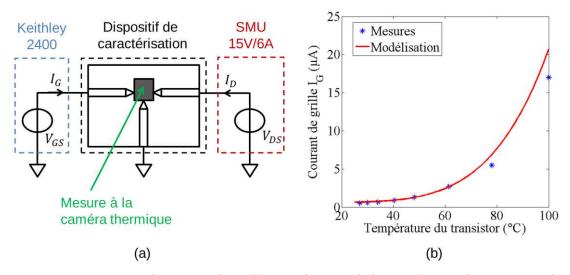

| Figure III. 22 : Mesure du courant de grille <i>IG</i> en fonction de la température de jonction <i>Tj</i> du |        |

| transistor : (a) banc de caractérisation (b) résultats de mesure et de modélisation                           | 86     |

| Figure III. 23 : Evolutions de $IG$ et de $\Delta T$ estimée durant les mesures de puissances dissipées dans  | le     |

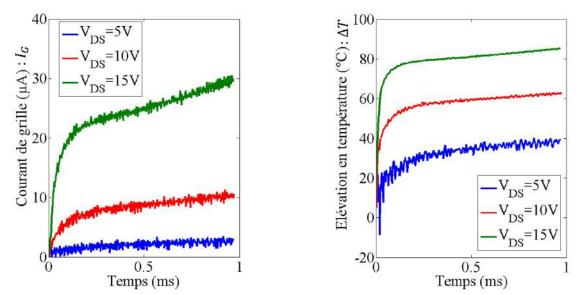

| transistor GaN ( $Ta = 23$ ° $C$ )                                                                            | 87     |

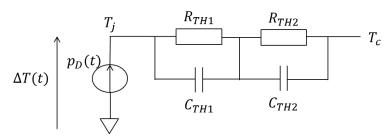

| Figure III. 24 : Modèle de Foster du second ordre                                                             | 87     |

| Figure III. 25 : Mesure et modélisation à partir de la fonction de transfert thermique du modèle de           |        |

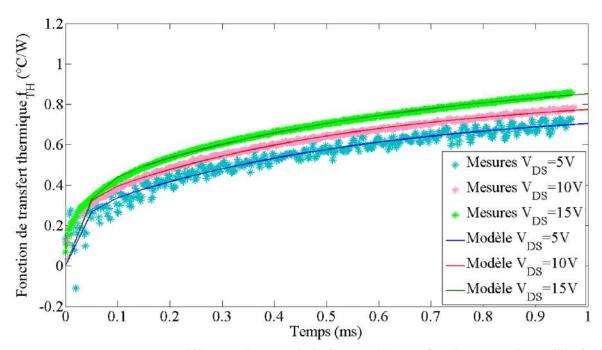

| Foster à deux constantes de temps pour différents VDS                                                         | 88     |

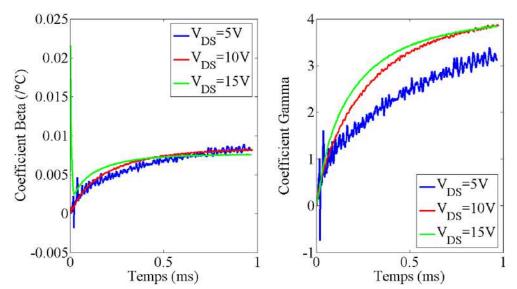

| Figure III. 26 : Extraction des valeurs initiales des paramètres $\beta$ et $\gamma$ à partir des résultats   |        |

| expérimentaux                                                                                                 | 89     |

| Figure III. 27 : Schéma de principe de la procédure d'optimisation pour la détermination des valeu            |        |

| des éléments du modèle thermique                                                                              |        |

| Figure III. 28 : Résultats d'optimisation et comparaison aux mesures : (a) modèle 1 (b) modèle 2              |        |

| Figure III. 29 : Modèle de Cauer du second ordre                                                              |        |

| Figure III. 30 : Impédance thermique transitoire normalisée du modèle proposé comparé aux donne               |        |

| constructeur pour des impulsions uniques, des impulsions répétées avec un rapport cyclique de 20              |        |

| des impulsions répétées avec un rapport cyclique de 50 %                                                      |        |

| Figure III. 31 : Implémentation du modèle thermique au sein du modèle électrique du transistor da             |        |

| logiciel ADS                                                                                                  |        |

| Figure III. 32 : Schéma de simulation pour la validation de l'implémentation du modèle                        |        |

| électrothermique du transistor GaN                                                                            | 93     |

| Figure III. 33 : Résultats de simulation de puissances dissipées avec le modèle électrothermique              |        |

| proposé et comparaison aux résultats expérimentaux et aux simulations avec le modèle constructe               | eur 93 |

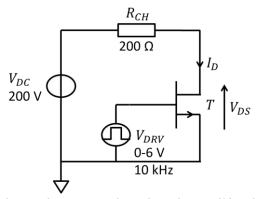

| Figure III. 34 : Banc de mesure de la résistance dynamique du transistor GaN [III.21]                         |        |

| Figure III. 35 : (a) Schéma de principe du modèle de résistance dynamique basé sur la compensation            |        |

| la tension grille-source (b) caractéristique $RDSon = f(VGS)$ [III.21]                                        |        |

| Figure III. 36 : Circuit de la tension de compensation à partir d'une cellule RC                              |        |

| Figure III. 37 : Schéma de principe de modélisation de la résistance dynamique par ajout d'une                |        |

| résistance de drain                                                                                           | 96     |

| Figure III. 38 : Circuit permettant l'obtention de la tension $Vr$ à partir d'une cellule RC                  |        |

| Figure III. 39 : Schéma d'implémentation d'une cellule du modèle de résistance dynamique dévelo               |        |

| dans ADS                                                                                                      |        |

| Figure III. 40 : Schéma de simulation pour l'analyse des modèles de résistance dynamique                      |        |

| Figure III. 41: Résultats de simulation obtenus au bout d'une seconde de simulation pour les deux             |        |

| modèles de résistance dynamique étudiés ( $Ta = 25^{\circ}C$ )                                                |        |

| moderes de resistance dynamique étudies (1 u 25 0)                                                            | 55     |

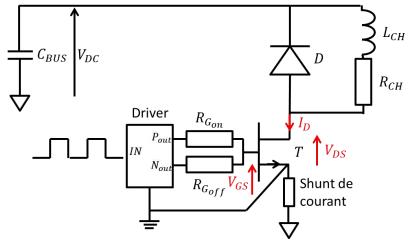

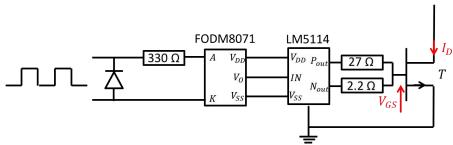

| Figure IV. 1 : Schéma électrique du banc de caractérisation Double Pulse                                      | 104    |

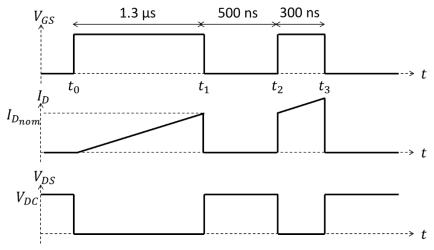

| Figure IV. 2 : Chronogrammes et formes d'onde du test Double Pulse                                            | 105    |

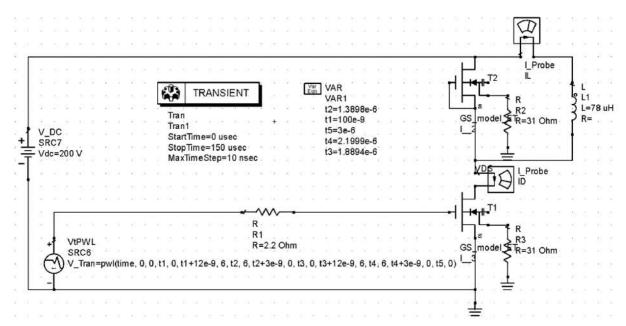

| Figure IV. 3 : Schéma de simulation du fonctionnement du test Double Pulse                                    | 106    |

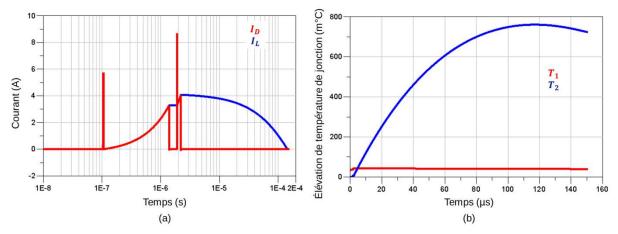

| Figure IV. 4: (a) Formes d'onde des courants ID et IL durant le test Double Pulse (b) Elévation en            |        |

| température des jonctions des transistors $T1$ et $T2$ avec $Ta = 25^{\circ}C$                                | 106    |

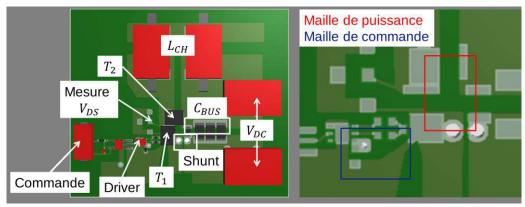

| Figure IV. 5 : Présentation du circuit Double Pulse conçu et mailles de commutation de puissance              | et de  |

| commande                                                                                                      |        |

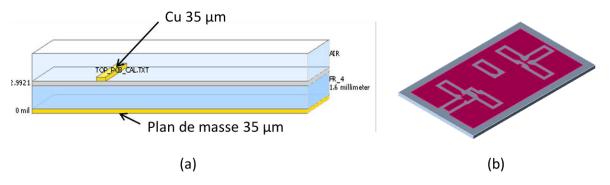

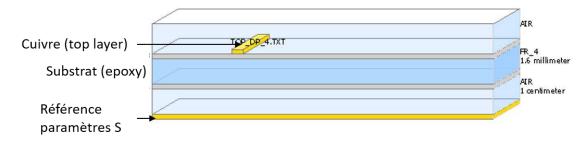

| Figure IV. 6 : Définition du substrat du circuit imprimé du banc de test Double Pulse                         | 107    |

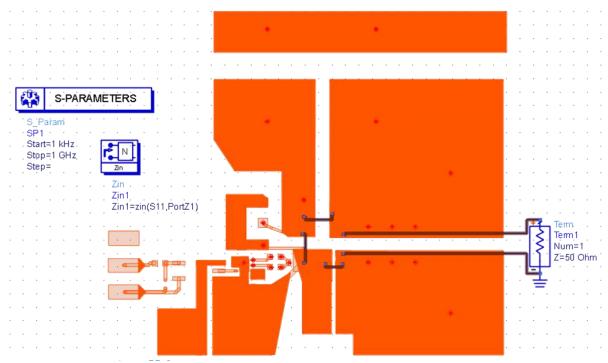

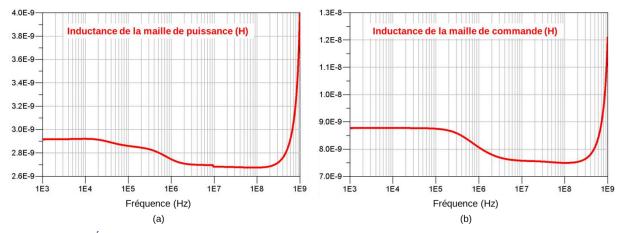

| Figure IV. 7 : Schéma de simulation en paramètres S pour la détermination de l'inductance de la ma             |      |

|----------------------------------------------------------------------------------------------------------------|------|

| de puissance                                                                                                   |      |

| Figure IV. 8 : Schéma de simulation en paramètres S pour la détermination de l'inductance de la ma             |      |

| de commande                                                                                                    |      |

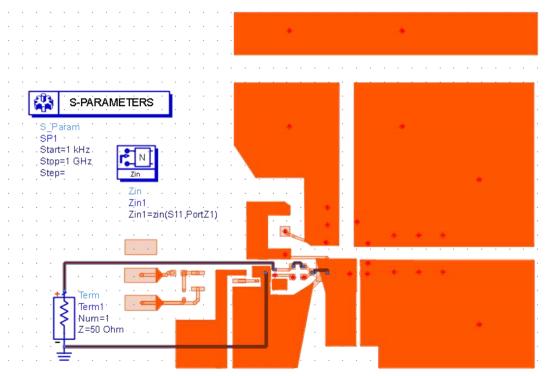

| Figure IV. 9 : Évolutions fréquentielles simulées des inductances des mailles (a) de puissance et (b) commande |      |

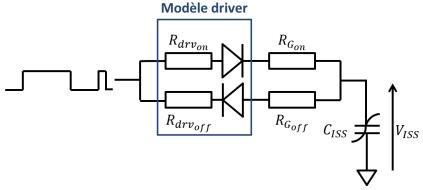

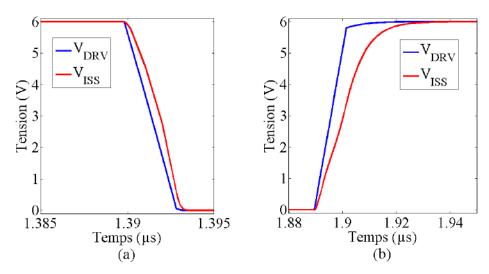

| Figure IV. 10 : Schéma de principe de la simulation ADS pour l'analyse du modèle proposé pour le driver        |      |

| Figure IV. 11 : Simulation du circuit de commande du transistor GaN : (a) au blocage (b) à la mise conduction  | en   |

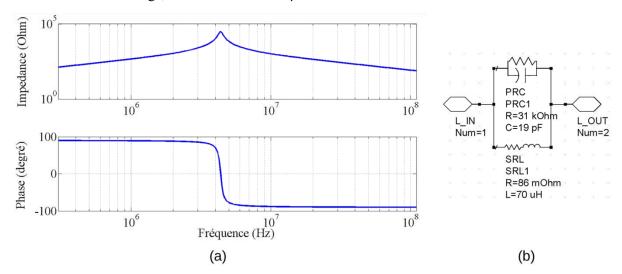

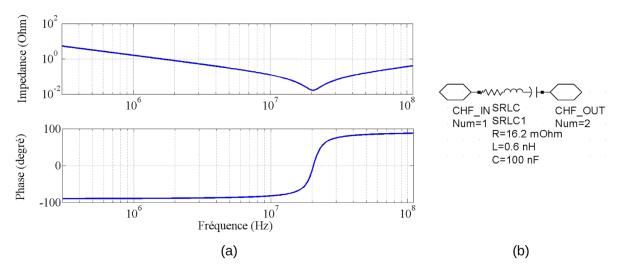

| Figure IV. 12 : Bobine équivalente <i>LCH</i> : (a) Impédance et phase (b) Modèle électrique                   | 110  |

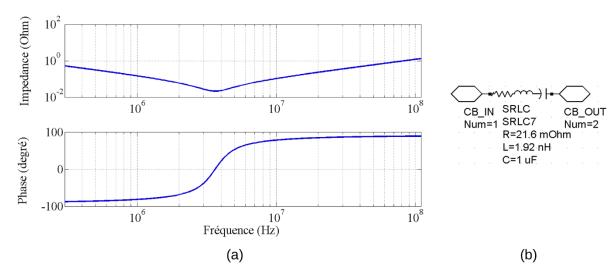

| Figure IV. 13 : Condensateur 1 μF du bus continu : (a) Impédance et phase (b) Modèle électrique                |      |

| Figure IV. 14 : Condensateur 100 nF du bus continu : (a) Impédance et phase (b) Modèle électrique              | 111  |

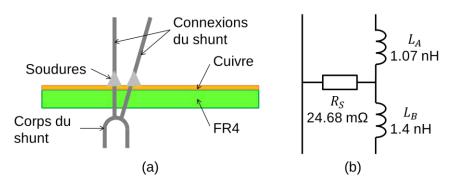

| Figure IV. 15 : Shunt de courant : (a) Schéma de fixation sur la carte Double Pulse (b) Modèle                 |      |

| électrique proposé                                                                                             | 111  |

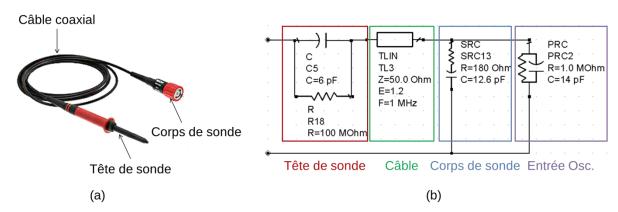

| Figure IV. 16 : Sonde de mesure de tension : (a) Présentation (b) Modèle électrique proposé                    | 112  |

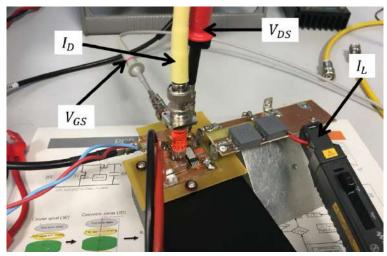

| Figure IV. 17: Présentation du banc de test Double Pulse et de son instrumentation de mesure                   | 112  |

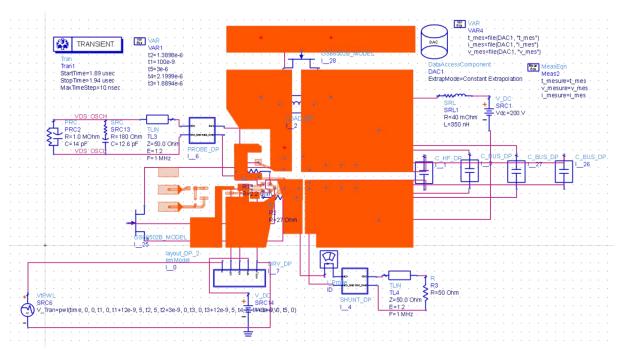

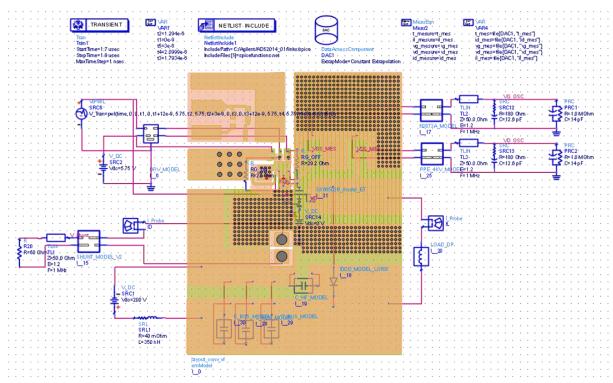

| Figure IV. 18 : Schéma de simulation ADS du circuit Double Pulse                                               | 113  |

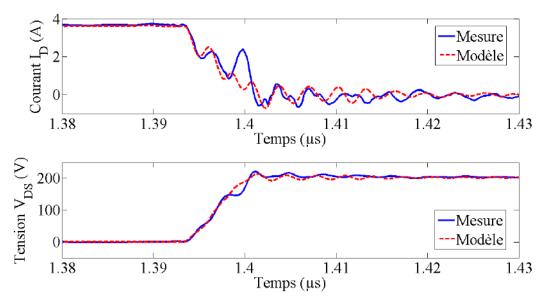

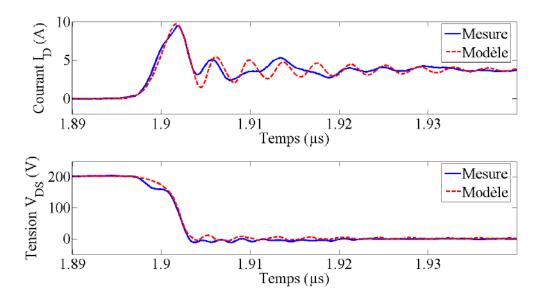

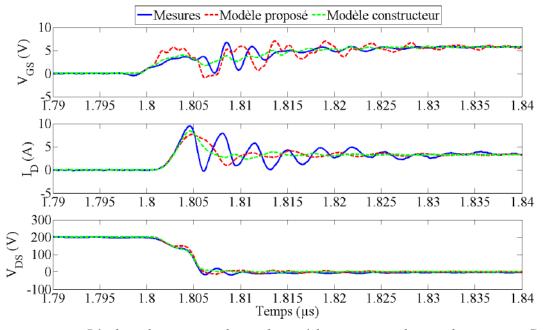

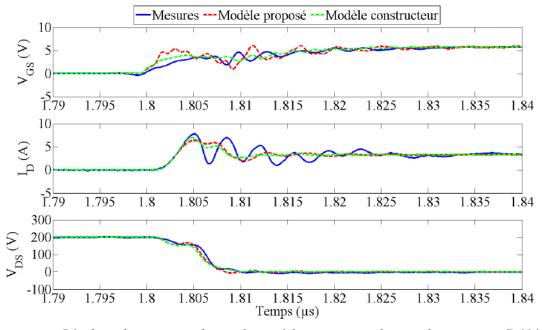

| Figure IV. 19: Résultats de mesure et de simulation au blocage du transistor T1                                | 114  |

| Figure IV. 20 : Résultats de mesure et de simulation à la mise en conduction du transistor T1                  | 114  |

| Figure IV. 21 : Schéma électrique du convertisseur DC/DC GaN/SiC                                               | 115  |

| Figure IV. 22 : Circuit de commande de la grille du transistor T                                               | 115  |

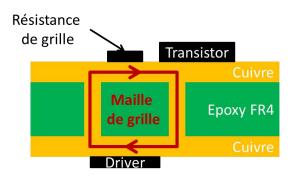

| Figure IV. 23 : Conception de la maille de grille en double face                                               | 116  |

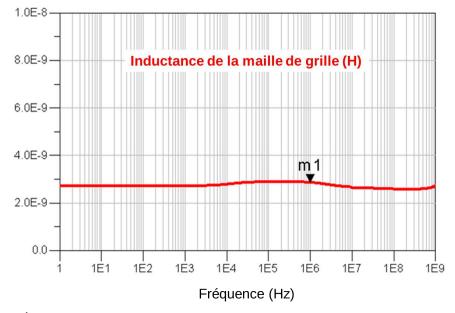

| Figure IV. 24 : Évolution fréquentielle de l'inductance de la maille de grille du convertisseur obtenu         | ıe   |

| en simulation avec ADS                                                                                         | 116  |

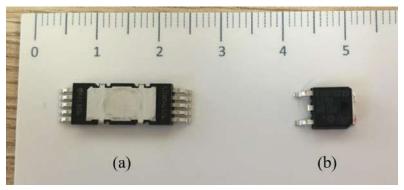

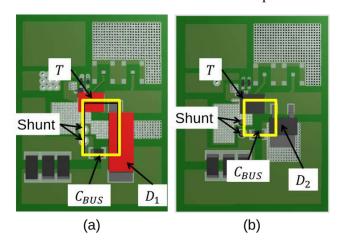

| Figure IV. 25 : Présentation des diodes Schottky SiC sélectionnées : (a) diode D1 (b) diode D2                 | 117  |

| Figure IV. 26: Conception de la maille de puissance: (a) avec la diode D1 (b) avec la diode D2                 | 117  |

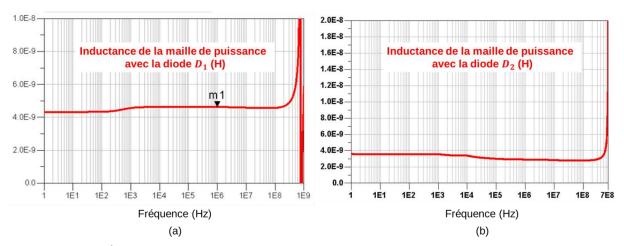

| Figure IV. 27 : Évolution fréquentielle de l'inductance parasite de la maille de puissance simulée en          | l    |

| utilisant ADS: (a) avec la diode D1 (b) avec la diode D2                                                       | 118  |

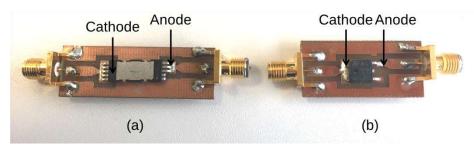

| Figure IV. 28 : Dispositifs de caractérisation des diodes : (a) D1 et (b) D2                                   | 118  |

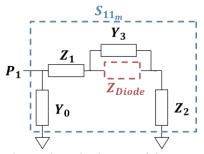

| Figure IV. 29 : Schéma équivalent du dispositif de caractérisation avec diode                                  | 118  |

| Figure IV. 30 : Schéma électrique équivalent d'une diode SiC                                                   | 119  |

| Figure IV. 31 : Extraction des éléments parasites de la diode D1                                               | 119  |

| Figure IV. 32 : Extraction des éléments parasites de la diode D2                                               | 120  |

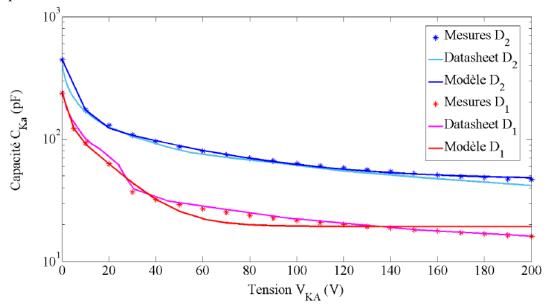

| Figure IV. 33 : Comparaison des évolutions des capacités CKa des diodes en fonction de VKA                     |      |

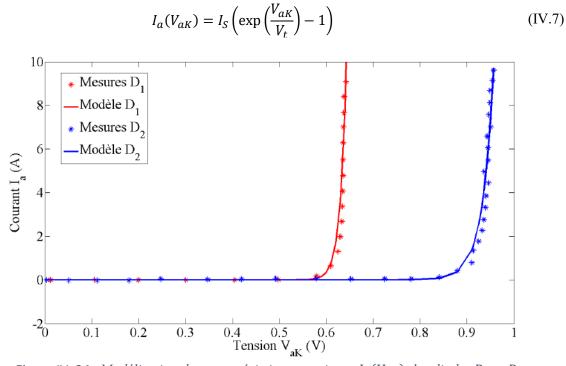

| Figure IV. 34 : Modélisation des caractéristiques statiques <i>IaVaK</i> des diodes <i>D</i> 1 et <i>D</i> 2   | 121  |

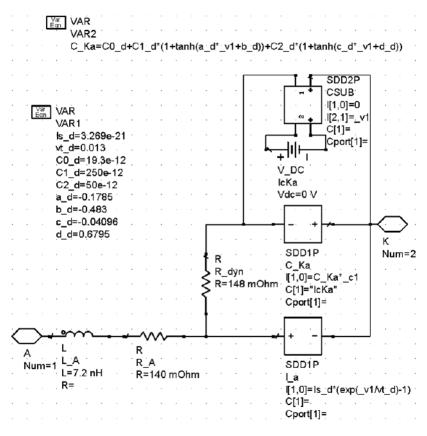

| Figure IV. 35 : Implémentation du modèle de diode dans ADS (exemple pour la diode D1)                          | 122  |

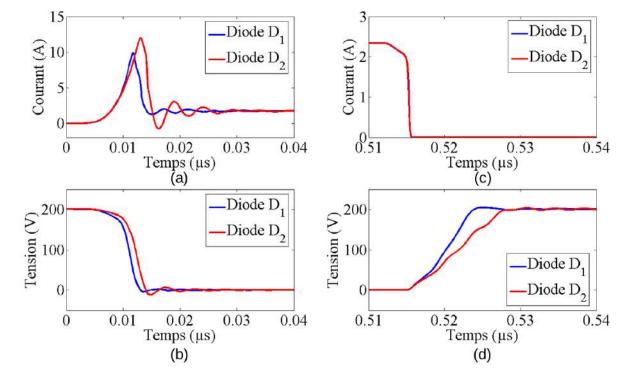

| Figure IV. 36 : Formes d'onde simulées pour les deux configurations de convertisseur : (a) Courant             |      |

| Icanal à la mise en conduction (b) Tension VDS à la mise en conduction (c) Courant Icanal au                   |      |

| blocage (d) Tension VDS au blocage                                                                             | 123  |

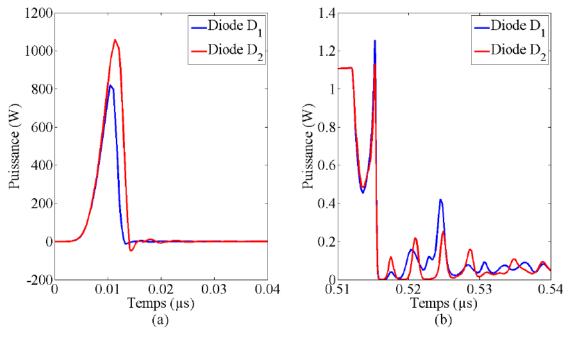

| Figure IV. 37 : Comparaison des pertes par commutation du transistor simulées pour les deux                    |      |

| configurations de convertisseur (a) à la mise en conduction (b) au blocage                                     |      |

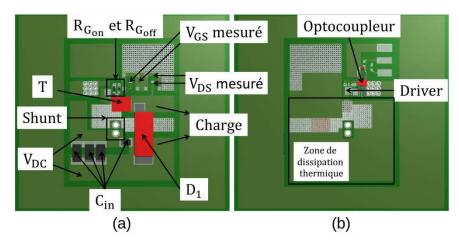

| Figure IV. 38 : Présentation de la version finale du convertisseur GaN/SiC : (a) Face du dessus (b) I          | Face |

| du dessous                                                                                                     |      |

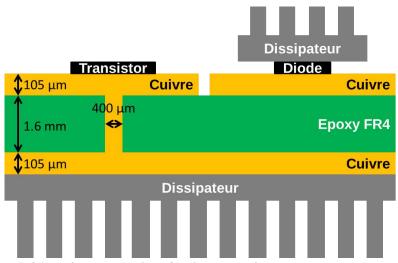

| Figure IV. 39 : Schéma de principe du refroidissement du convertisseur avec vias thermiques                    |      |

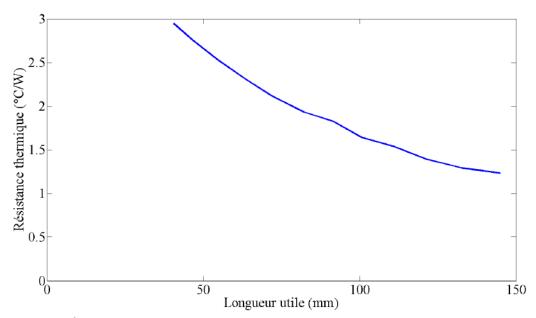

| Figure IV. 40 : Évolution de la résistance thermique du dissipateur en fonction de la longueur utile .         | 126  |

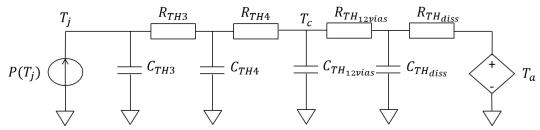

| Figure IV. 41 : Schéma de simulation pour l'estimation de la température de fonctionnement du                  |      |

| transistor GaN au sein du convertisseur GaN/SiC                                                                | 126  |

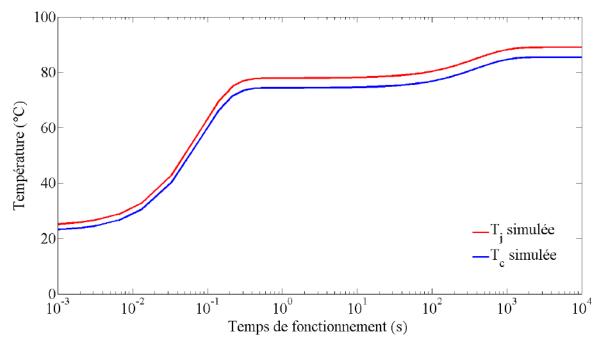

| Figure IV. 42 : Simulation de la température de boitier et de jonction du transistor GaN lors de son |     |

|------------------------------------------------------------------------------------------------------|-----|

| fonctionnement au sein du convertisseur GaN/SiC                                                      | 127 |

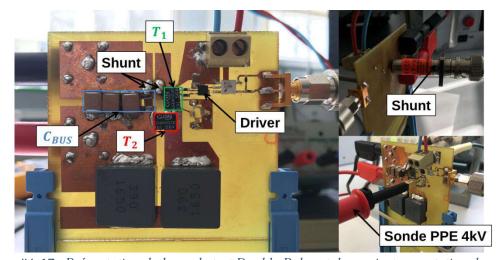

| Figure IV. 43: Convertisseur GaN/SiC en fonctionnement Double Pulse avec son instrumentation de      | e   |

| mesure et indication des grandeurs mesurées                                                          |     |

| Figure IV. 44 : Schéma de simulation du convertisseur GaN/SiC en fonctionnement Double Pulse         | 128 |

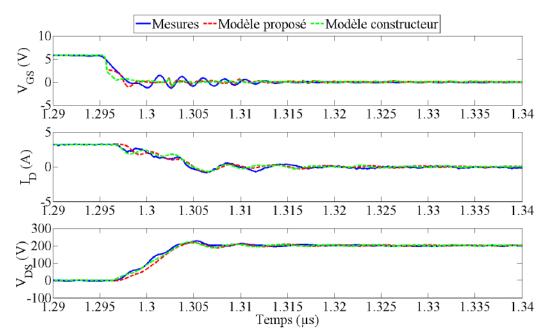

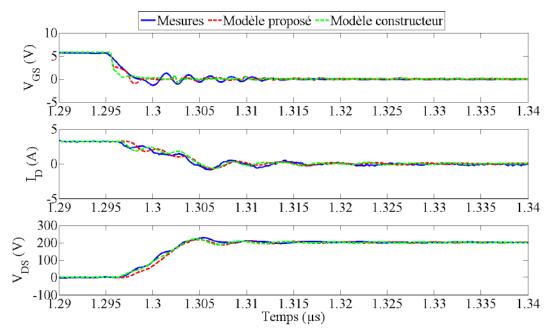

| Figure IV. 45: Résultats de mesure et de simulation au blocage du transistor GaN                     | 129 |

| Figure IV. 46 : Résultats de mesure et de simulation à la mise en conduction du transistor GaN       | 129 |

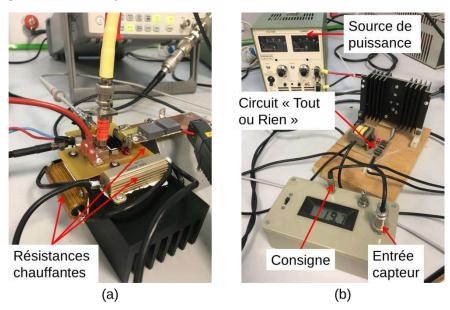

| Figure IV. 47 : (a) Convertisseur en fonctionnement Double Pulse avec résistances chauffantes (b)    |     |

| Système de régulation de température                                                                 | 130 |

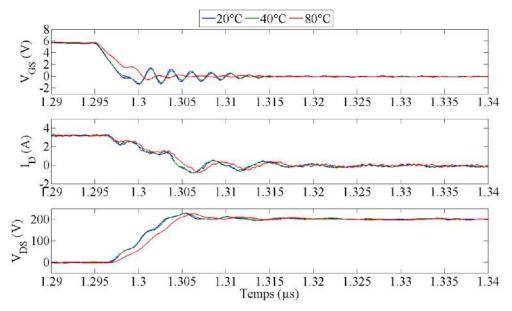

| Figure IV. 48 : Résultats de mesure au blocage du transistor GaN à différentes températures de jonct | ion |

|                                                                                                      | 130 |

| Figure IV. 49 : Résultats de mesure à la mise en conduction du transistor GaN à différentes          |     |

| températures de jonction                                                                             | 131 |

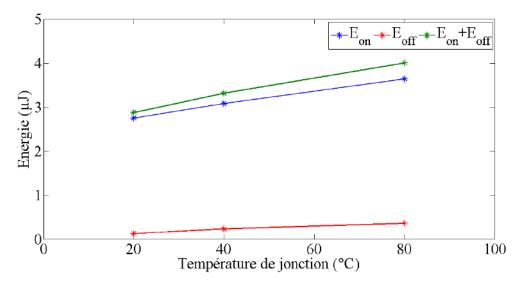

| Figure IV. 50 : Evolution des énergies de commutation à la mise en conduction et au blocage du       |     |

| transistor en fonction de la température                                                             | 131 |

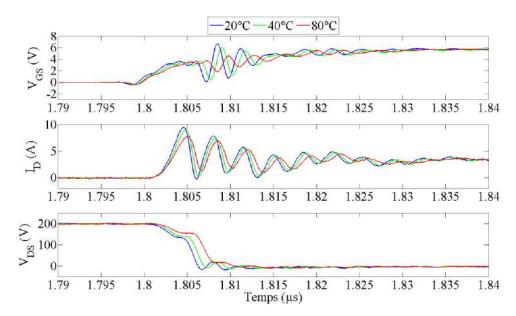

| Figure IV. 51 : Résultats de mesure et de simulation au blocage du transistor GaN à 40 °C            | 132 |

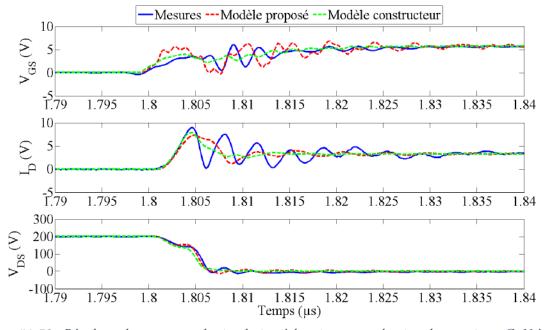

| Figure IV. 52 : Résultats de mesure et de simulation à la mise en conduction du transistor GaN à 40  | °C  |

|                                                                                                      | 132 |

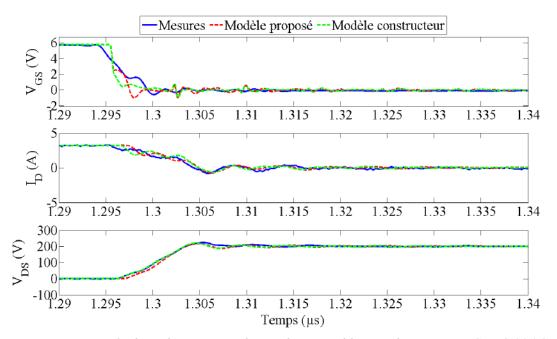

| Figure IV. 53 : Résultats de mesure et de simulation au blocage du transistor GaN à 80 °C            | 133 |

| Figure IV. 54 : Résultats de mesure et de simulation à la mise en conduction du transistor GaN à 80  | °C  |

|                                                                                                      | 133 |

| Figure IV. 55 : Convertisseur GaN/SiC en fonctionnement répétitif avec son instrumentation de mes    | ure |

|                                                                                                      | 134 |

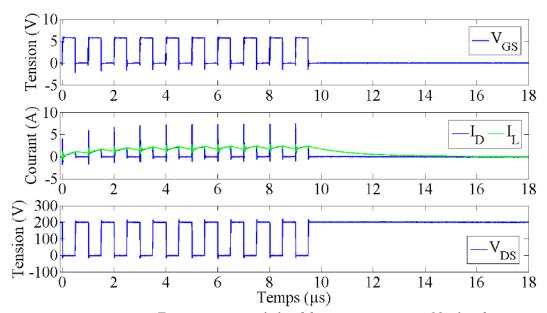

| Figure IV. 56 : Fonctionnement répétitif du convertisseur sur 10 périodes                            | 134 |

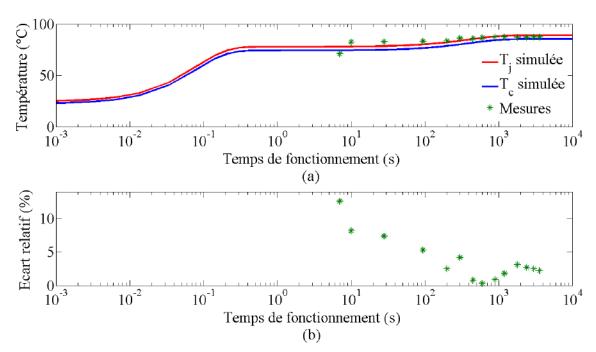

| Figure IV. 57 : Mesure et simulation de la température du transistor GaN en fonctionnement au sein   | du  |

| convertisseur : (a) Comparaison entre mesure et simulation (b) écart relatif des élévations de       |     |

| température entre mesure et simulation de <i>Tj</i>                                                  | 135 |

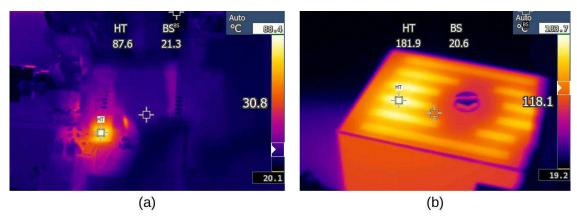

| Figure IV. 58 : Mesure de la température après une heure de fonctionnement du convertisseur : (a) su | ur  |

| le transistor GaN (b) sur la résistance de charge                                                    | 135 |

# Liste des tableaux

Tableau I. 1 : Propriétés des matériaux semi-conducteurs utilisés en électronique de puissance [I.23] 15

| Tableau II. 1 : Principales caractéristiques du transistor GaN GS66502B                           |

|---------------------------------------------------------------------------------------------------|

| Tableau II. 2 : Paramètres des modèles de la figure II.31                                         |

| Tableau II. 3 : Paramètres du modèle de la figure II.32                                           |

| Tableau II. 4 : Extraction des résistances d'accès du transistor GS66502B                         |

| Tableau II. 5 : Extraction des inductances d'accès par la méthode Cold FET                        |

| Tableau II. 6: Extraction des inductances d'accès du transistor GS66508B                          |

| Tableau II. 7: Extraction des résistances d'accès du transistor GS66508B                          |

| Tableau II. 8 : Températures de jonction mesurées pour différents courants de drain               |

| Tableau II. 9 : Extraction de RS et RD en fonction de la température de jonction Tj               |

| Tableau II. 10 : Paramètres des modèles des résistances RD et RS en fonction de Tj                |

| Tableau III. 1 : Paramètres des modèles de capacités inter-électrodes                             |

| Tableau III. 2 : Paramètres du modèle de la source de courant de drain                            |

| Tableau III. 3 : Paramètres du modèle de la source de courant de grille                           |

| Tableau III. 4 : Paramètres initiaux du modèle thermique de Foster                                |

| Tableau III. 5 : Paramètres du modèle 1                                                           |

| Tableau III. 6 : Paramètres du modèle 2                                                           |

| Tableau III. 7 : Paramètres du modèle thermique de Cauer                                          |

| Tableau III. 8 : Paramètres des éléments du modèle par compensation de la tension grille-source 9 |

| Tableau III. 9 : Paramètres des éléments du modèle par ajout d'une résistance de drain            |

| Tableau IV. 1 : Liste des composants du banc de test Double Pulse                                 |

| Tableau IV. 2 : Extraction des éléments parasites des diodes <i>D</i> 1 et <i>D</i> 2             |

| Tableau IV. 3 : Paramètres des modèles CKaVKA des diodes D1 et D2                                 |

| Tableau IV. 4 : Paramètres des modèles <i>IaVaK</i> des diodes <i>D</i> 1 et <i>D</i> 2           |

| Tableau IV. 5 : Pertes moyennes et énergie perdue par le transistor sur un cycle                  |

## Glossaire

### Paramètres des transistors

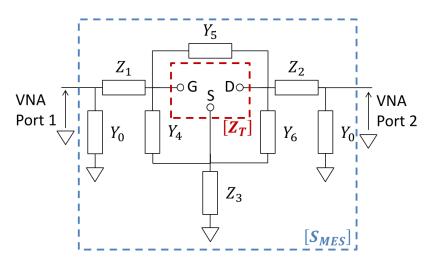

$[S_{MEAS}]$ : Matrice des paramètres S mesurés sur le transistor

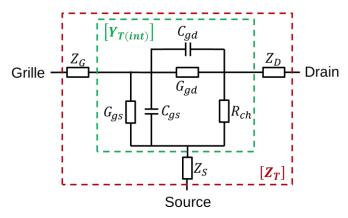

$[Z_T]$ : Matrice impédance du transistor GaN

$C_{ds}$ ,  $C_{DS}$ : Capacités entre grille et source respectivement intrinsèque et extrinsèque du transistor

$C_{gd}$ ,  $C_{GD}$ : Capacités entre grille et source respectivement intrinsèque et extrinsèque du transistor

$C_{gs}$ ,  $C_{GS}$ : Capacités entre grille et source respectivement intrinsèque et extrinsèque du transistor

$C_{ISS}$ : Capacité d'entrée du transistor

$C_{OSS}$ : Capacité de sortie du transistor

$C_{PD}$ : Capacité de plot coté drain du transistor

$C_{PG}$ : Capacité de plot coté grille du transistor

C<sub>RSS</sub>: Capacité Miller du transistor

$C_{TH1}$ ,  $C_{TH2}$ : Capacités thermiques du modèle de Foster pour le transistor GaN

C<sub>TH3</sub>, C<sub>TH4</sub>: Capacités thermiques du modèle de Cauer pour le transistor GaN

$I_{canal}$ : Courant dans le canal du transistor

$I_G$ : Courant de grille externe du transistor

$I_d$ : Source de courant de drain intrinsèque du transistor

$i_D$ ,  $I_D$ : courant de drain externe du transistor

$I_a$ : Source de courant de grille intrinsèque du transistor

$g_{ds}$ : Conductance de sortie du transistor

$g_{ad}$ : Conductance entre grille et drain du transistor

$g_{qs}$ : Conductance entre grille et source du transistor

$g_m$ : Transconductance du transistor

$L_D$ : Inductance d'accès de drain du transistor

$L_G$ : Inductance d'accès de grille du transistor

$L_{KS}$ : Inductance de la source Kelvin du transistor GaN GS66508B

$L_{PS}$ : Inductance de la source coté Puissance du transistor GaN GS66508B

$L_S$ : Inductance d'accès de source du transistor

$p_D$ ,  $P_D$ : Puissance dissipée par le transistor GaN

$Q_G$ : Charge totale de la grille du transistor

$R_{d_{DS(on)}}$ : Résistance dynamique du transistor GaN

$R_D$ : Résistance d'accès de drain du transistor

$R_{DS}$ : Résistance drain-source du transistor

$R_G$ : Résistance d'accès de grille du transistor

$R_{KS}$ : Résistance de la source Kelvin du transistor GaN GS66508B

R<sub>PS</sub>: Résistance de la source coté Puissance du transistor GaN GS66508B

$R_S$ : Résistance d'accès de source du transistor

$R_{TH1},\,R_{TH2}$ : Résistances thermiques du modèle de Foster pour le transistor GaN

$R_{TH3}$ ,  $R_{TH4}$ : Résistances thermiques du modèle de Cauer pour le transistor GaN

R<sub>ch</sub>: Résistance du canal du transistor GaN

$R_{gd}$  : Résistance intrinsèque entre grille et source du transistor

$R_{as}$ : Résistance intrinsèque entre grille et source du transistor

$R_{on}$ ,  $R_{DS(on)}$ : Résistance drain-source à l'état passant du transistor

$T_c$ : Température du boitier du transistor GaN

$T_i$ : Température de la jonction du transistor GaN

$V_{DG}$ : Tension drain-grille externe du transistor

$V_{DS(on)}$ : Tension drain-source externe à l'état passant du transistor

$V_{DS}$ : Tension drain-source externe du transistor

$V_{GS}$ : Tension grille-source externe du transistor

$V_{PK}$ : Surtension de  $V_{DS}$

$V_{TH}$ : Tension de seuil du transistor

$V_{ds}$ : Tension drain-source interne du transistor

$V_{as}$ : Tension grille-source interne du transistor

$Y_{ds}$ : Admittance intrinsèque entre drain et source

$Y_{gd}$ : Admittance intrinsèque entre grille et drain

$Y_{gm}$ : Admittance liée à la transconductance du transistor

$Y_{as}$ : Admittance intrinsèque entre grille et source

$Z_D$ : Impédance d'accès de drain

$Z_G$ : Impédance d'accès de grille

$Z_S$ : Impédance d'accès de source

### Paramètres des diodes

$C_d$ : Capacité inter-électrode de la diode

$I_a$ : Source de courant intrinsèque d'anode

$i_A$ : Courant d'anode externe

$L_A$ : Inductance extrinsèque de la diode

$R_A$ : Résistance extrinsèque de la diode

$R_{AK}$ : Résistance à l'état passant de la diode

$R_{LEAK}$ : Résistance de la diode en conduction inverse

$R_{dvn}$ : Résistance de la caractéristique dynamique de la diode

$V_{AK}$ : Tension anode-cathode externe de la diode

$V_{aK}$ : Tension anode-cathode interne de la diode

$V_{OFF}$ : Tension de blocage

$V_{RM}$ : Tension inverse maximale de la diode

$V_T$ : Tension de seuil de la diode

### Paramètres divers

$C_{RUS}$ : Condensateur équivalent du bus continu

$f_{SW}$ : Fréquence de commutation

$I_{CH}$ : Courant dans la charge

$L_{d_{ext}}$ : Inductance parasite de la maille de commutation coté drain

$L_{g_{ext}}$ : Inductance parasite de la maille de commutation coté grille

$L_{S_{ext}}$ : Inductance parasite de la maille de commutation coté source

$\mathcal{L}_{CH}$  : Inductance de la charge du convertisseur

$L_p$ : Inductance parasite de la maille de commutation

$R_{G_{off}}$ : Résistance du circuit de commande de grille pour le blocage du transistor

$R_{G_{on}}$ : Résistance du circuit de commande de grille pour la mise en conduction du transistor

$R_{d_{ext}}$ : Résistance parasite de la maille de commutation coté drain

$R_{q_{ext}}$ : Résistance parasite de la maille de commutation coté grille

$R_{S_{ext}}$ : Résistance parasite de la maille de commutation coté source

$R_{CH}$ : Résistance de la charge du convertisseur

$S_{ij}$ : Paramètre S résultant d'une injection au port j et mesure au port i

T : Période de commutation

$T_a$ : Température ambiante

$V_{DC}$ : Tension du bus continu

$V_{DRV}$ : Tension de sortie du driver

$Y_{ij}$ : Paramètre admittance résultant d'une injection au port j et mesure au port i

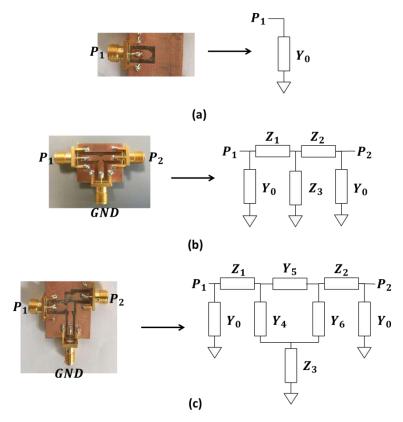

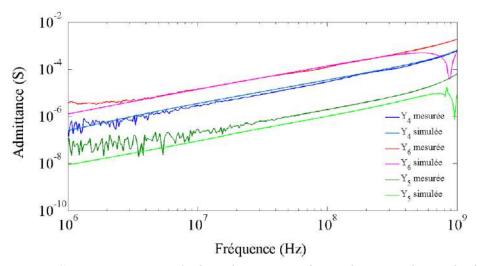

$Y_0$ : Admittance des couplages entre une ligne de transmission et le plan de masse sur PCB

Y<sub>4</sub>, Y<sub>5</sub>, Y<sub>6</sub>: Admittances des couplages entres les lignes de transmission sur PCB

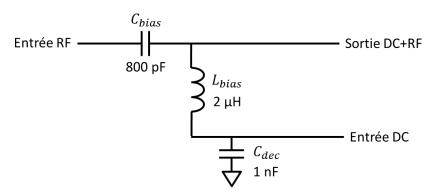

$Z_{bias}$ : Impédance du Té de polarisation

$Z_{C_{LT}}$ : Impédance caractéristique de la ligne de transmission

$Z_{C_{SMA}}$ : Impédance caractéristique du connecteur SMA

$Z_{dip}$ : Impédance d'un dipôle

$Z_{ij}$ : Paramètre impédance résultant d'une injection au port j et mesure au port i

$Z_0$ : Impédance caractéristique d'un port du VNA

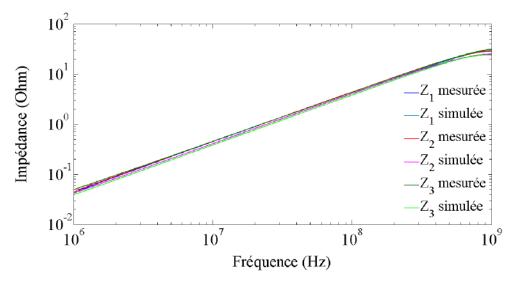

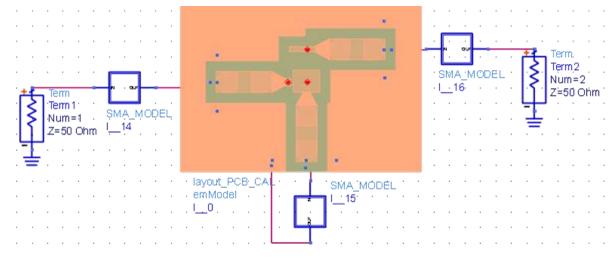

$Z_1, Z_2, Z_3$ : Impédances propres des lignes de transmission sur PCB

$\Delta T$ : Élévation de la température de jonction d'un semi-conducteur par rapport à la température ambiante

$\alpha$ : Portion de la résistance de canal du transistor situé entre grille et source

$\beta$ : Coefficient électrothermique du modèle 1

γ : Coefficient électrothermique du modèle 2

$\omega$ : Vitesse angulaire, pulsation

## Introduction générale

Le travail de thèse présenté dans ce manuscrit s'inscrit dans le cadre d'une collaboration entre le Laboratoire d'Electrotechnique et d'Electronique de Puissance (L2EP) et l'Institut d'Electronique, de Microélectronique et de Nanotechnologie (IEMN). Ces deux établissements de recherche ayant souhaité mettre en commun leur savoir-faire concernant la thématique de l'électronique de puissance haute fréquence. Dans ce contexte, les travaux de recherche se sont déroulés d'octobre 2016 à septembre 2019 au sein de l'université de Lille.

### Contexte scientifique

L'augmentation de la densité de puissance des convertisseurs statiques répond à un besoin de miniaturisation de plus en plus répandu, en particulier pour les applications embarquées dans lesquelles la puissance requise est en constante augmentation alors que la masse et l'encombrement des systèmes visent à être réduits. L'augmentation de la fréquence de commutation des dispositifs à semi-conducteurs de puissance offre la possibilité de réduire le volume et la masse des éléments passifs des convertisseurs. Cependant, avec l'utilisation des composants de puissance classiques à base de Silicium (Si), cette montée en fréquence est synonyme de pertes plus élevées et par conséquence une dégradation du rendement des convertisseurs ainsi que de la nécessité de systèmes de refroidissement plus encombrants. Les semi-conducteurs de puissance dits « grand gap » et notamment ceux à base de Nitrure de Gallium (GaN) présentent des propriétés physiques très attractives pour des applications en électronique de puissance haute fréquence. Récemment, des transistors de puissance GaN encapsulés sont disponibles sur le marché et leur capacité à commuter à des fréquences supérieures au mégahertz sans dégradation du rendement a fait l'objet de diverses études ces dernières années. Néanmoins les temps de commutation très courts (de l'ordre de quelques nanosecondes) de ces transistors GaN en font inévitablement des générateurs de perturbations électromagnétiques et les rendent sensibles à leur environnement de fonctionnement (surtensions, surintensités, risques d'instabilité...). Il est alors nécessaire de passer par différentes étapes de conception basées sur des simulations avant la réalisation de convertisseurs statiques haute fréquence à base de GaN. Pour ce faire, des modèles de transistors GaN maitrisés, fiables et précis y compris à des fréquences élevées sont des outils nécessaires.

### Objectifs de la thèse

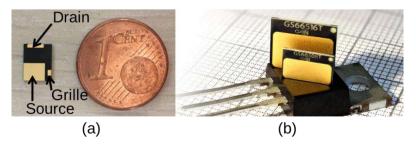

En lien avec le contexte décrit précédemment, l'objectif principal de ce travail de thèse est de proposer une méthodologie complète pour une modélisation électrothermique et comportementale de transistors de puissance GaN encapsulés. L'étude a été menée sur un transistor GaN commercialisé par la société GaN Systems®, le composant GS66502B 650 V et 7,5 A. La méthode de modélisation proposée est basée uniquement sur des caractérisations non-intrusives, non-dépendantes de données technologiques. Elle utilise notamment les mesures de paramètres S, ce qui constitue une approche innovante permettant de déterminer un schéma équivalent précis du composant. Le modèle proposé est implémenté dans le logiciel Advanced Design System (ADS) et utilisé lors de simulations pour la conception d'un convertisseur statique fonctionnant à 1 MHz. Les fonctionnalités d'ADS pour la modélisation fine du convertisseur sont également mises en avant.

### Organisation du manuscrit

Le premier chapitre de ce manuscrit présente une introduction à la modélisation des transistors de puissance GaN et à la conception des convertisseurs statiques haute fréquence. Ce chapitre est divisé en trois grandes parties. La première a pour objectif de détailler davantage les attentes liées aux semi-conducteurs de puissance au sein des convertisseurs statiques ainsi que de présenter un bref état de l'art concernant les avancées technologiques sur la conception de convertisseurs à forte densité de puissance. Une seconde partie démontre les intérêts liés au GaN par rapport aux autres matériaux semi-conducteurs pour l'électronique de puissance haute fréquence ainsi qu'un état de l'art des technologies de transistors de puissance GaN et leurs performances. Enfin, la dernière partie du chapitre traite des techniques de modélisation des composants de puissance, découlant sur le modèle électrothermique qui sera utilisé pour le transistor GaN étudié.

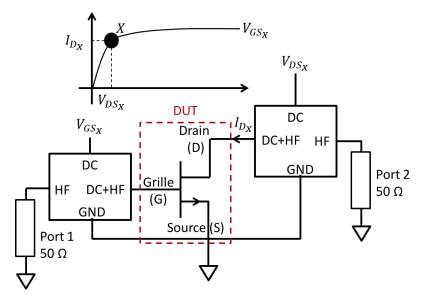

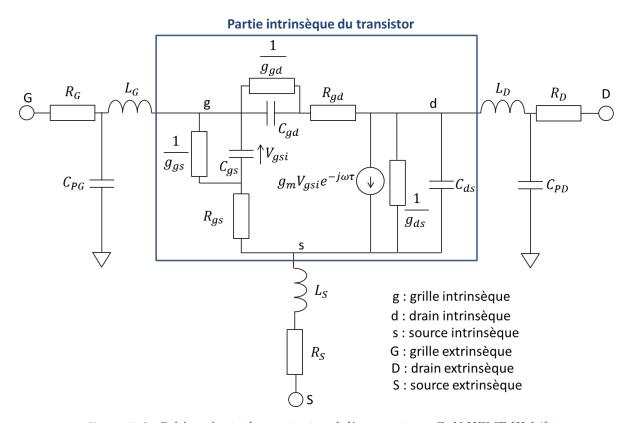

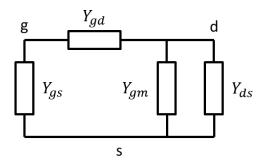

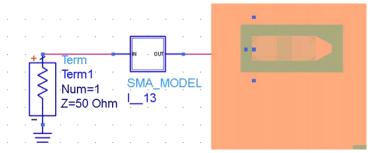

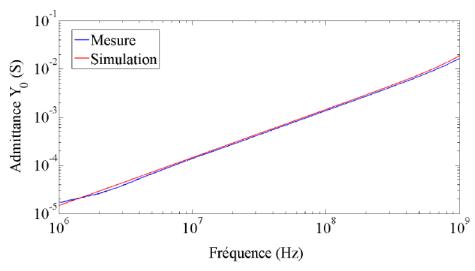

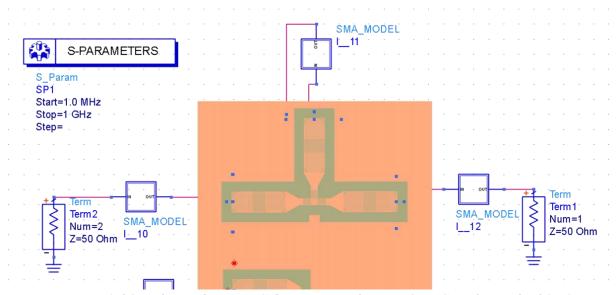

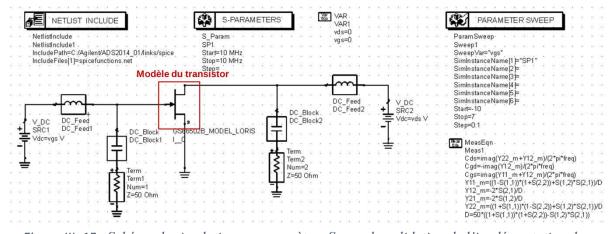

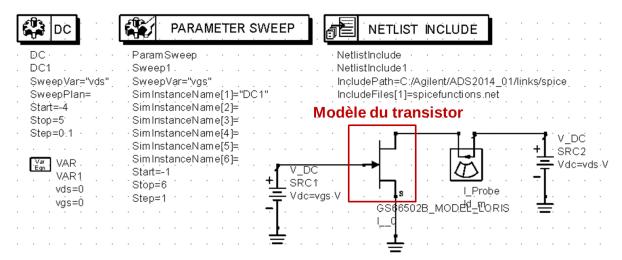

Dans le second chapitre, des caractérisations sur la plage de fréquences 1 MHz – 1 GHz basées sur la mesure des paramètres S du transistor GaN sont mises en œuvre afin d'extraire les éléments résistifs, inductifs et capacitifs du modèle du composant. Ce chapitre est divisé en trois parties. La première présente les dispositifs de caractérisation réalisés sur circuit imprimé pour la mesure des paramètres S du transistor dans son boitier ainsi que pour la polarisation du composant sous de fortes tensions et pour de forts courants. Une procédure de calibration spécifique basée sur des schémas équivalents est proposée et mise en application. La seconde partie présente les résultats obtenus pour la détermination des résistances et inductances liées aux accès à la partie interne du transistor. La dépendance en température des résistances d'accès est également étudiée dans cette partie et une méthode d'extraction utilisant les dispositifs de caractérisation développés est proposée. Enfin, la dernière partie du chapitre présente les résultats obtenus pour la détermination des capacités inter-électrodes en fonction des tensions grille-source et drain-source.

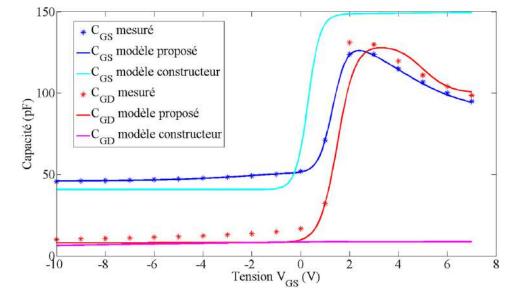

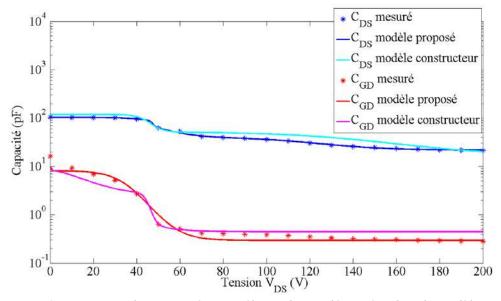

Suite aux résultats du second chapitre, la modélisation non linéaire des capacités inter-électrodes en fonction des tensions présentes à leurs bornes fait l'objet de la première partie du troisième chapitre. Des caractérisations I-V en régime continu et pulsé sont également menées dans cette première partie afin de déterminer des modèles non linéaires des sources de courant de grille et de drain. Le modèle électrique complet du transistor de puissance GaN encapsulé est implémenté dans le logiciel ADS et testé au travers de différentes simulations. Un modèle thermique du transistor GaN, basé sur des mesures de puissances dissipées et une procédure d'optimisation, est proposé dans la seconde partie de ce troisième chapitre. Ce modèle est validé par comparaison entre l'impédance thermique transitoire simulée et celle fournie dans la documentation technique du composant. Le modèle thermique est ensuite ajouté au modèle électrique du transistor afin d'établir le modèle électrothermique dans le logiciel ADS. Enfin, la dernière partie présente les travaux réalisés sur la modélisation des phénomènes de résistance dynamique présents au sein des transistors de puissance GaN. Ce travail est une contribution aux travaux de recherche menés entre le L2EP et l'Université de Nottingham.

Le quatrième et dernier chapitre porte sur l'utilisation du modèle de transistor développé pour la conception d'un convertisseur statique haute fréquence. Dans un premier temps, un circuit Double Pulse est réalisé afin de confronter les résultats de mesure aux résultats de simulation utilisant le modèle proposé. L'utilisation des fonctionnalités d'ADS pour la modélisation du circuit, y compris du circuit imprimé, est détaillée dans cette partie. L'analyse des formes d'onde lors des commutations permettra de valider les méthodes de modélisation. La conception d'un convertisseur DC/DC de 200 W fonctionnant à 1 MHz et basé sur une cellule de commutation transistor GaN – diode Schottky SiC fait l'objet de la seconde partie du chapitre. L'utilisation du modèle du transistor GaN proposé servira quant au choix de la diode SiC la plus adaptée à l'application. Une modélisation thermique du circuit de refroidissement du transistor GaN est également réalisée afin de prédire l'évolution temporelle de la

### Introduction générale

température du composant lors de son fonctionnement au sein du convertisseur. Ces estimations sont validées dans la troisième partie de ce chapitre lors du fonctionnement pendant une heure du convertisseur statique. La dernière partie du chapitre présente un banc expérimental permettant la réalisation de test en Double Pulse à différentes températures du transistor GaN afin de valider le modèle électrothermique proposé.

Finalement, une conclusion générale des travaux engagés dans cette thèse ainsi que les perspectives seront présentées à la fin du manuscrit.

### Introduction

Depuis ces dernières décennies, des marchés spécifiques comme l'automobile, l'aéronautique, les datacenters et autres technologies de pointe requièrent des systèmes de conversion d'énergie et occupant des volumes restreints. Dans une optique d'intégration des dispositifs, la montée en fréquence des convertisseurs statiques permet de réduire le volume des éléments passifs. La première partie de ce chapitre vise à détailler davantage ce contexte, les attentes quant aux semi-conducteurs de puissance ainsi qu'un état de l'art non exhaustif des avancées scientifiques et technologiques vers la conception de convertisseurs de puissance à forte densité de puissance.

Les transistors de puissance à base de nitrure de gallium (GaN) présentent un fort potentiel pour le développement de convertisseurs fonctionnant à hautes fréquences, notamment grâce à leur temps de commutation très court comparativement à leurs homologues en silicium. La seconde partie de ce chapitre offrira plus de détails quant aux avantages du GaN sur les autres matériaux semi-conducteurs utilisés en électronique de puissance pour des applications à hautes fréquences, ainsi qu'un état de l'art des technologies de transistors de puissance GaN existantes et leurs performances.

Cependant les faibles temps de commutation des transistors GaN les rendent sensibles à leur environnement de fonctionnement. Ainsi, la conception de convertisseurs haute fréquence à base de GaN nécessite des étapes de prototypage et d'analyse de performances par simulation, exigeant des modèles de composants prédictifs et fiables. La dernière partie de ce premier chapitre fait état de l'art des techniques de modélisation des transistors GaN qui serviront de base d'étude pour les travaux de recherche présentés dans ce manuscrit.

# I.1. Les composants semi-conducteurs pour la conversion d'énergie à hautes fréquences

I.1.1. Présentation de composants semi-conducteurs en électronique de puissance I.1.1.1. Contexte

De nombreuses applications réclament des alimentations spécifiques à haut rendement réalisées à partir de sources d'énergie de caractéristiques fixes. La conversion de l'énergie électrique consiste en la transformation du signal électrique (amplitude, fréquence, phase) fourni par une source pour l'adapter à la charge [I.1], [I.2]. Le champ d'application de l'électronique de puissance s'étend aujourd'hui à de nombreux sujets d'actualité parmi lesquels on peut citer plusieurs applications en lien avec les thématiques de recherche du laboratoire L2EP:

- Les convertisseurs DC/DC pour le transport électrique au sein des réseaux Haute Tension HVDC (Modular Multilevel Converter (MMC))

- Le stockage hybride pour la traction électrique (convertisseurs pour l'hybridation des sources d'énergie)

- Les convertisseurs intégrés pour la commande rapprochée des machines électriques (projet Convertisseur d'Energie Intégré et Intelligent (CE2I))

- Les alimentations dans les systèmes embarqués (alimentations à découpage, chargeurs électriques compacts...)

L'électronique de puissance effectue le lien entre source et charge par instants au moyen de composants semi-conducteurs jouant le rôle d'interrupteurs électroniques [I.3], [I.4]. L'efficacité énergétique des convertisseurs est directement liée aux caractéristiques de ces semi-conducteurs qui peuvent être classés en trois catégories :

- Les interrupteurs non commandés : les diodes

- Les interrupteurs commandés à la fermeture uniquement : les thyristors

- Les interrupteurs commandés à l'ouverture et à la fermeture : les transistors et les thyristors « Gate Turn-Off » (GTO)

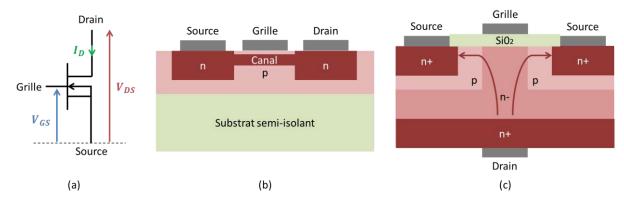

Parmi les transistors, on retrouve deux types: les transistors bipolaires et les transistors unipolaires, dits à effet de champ. Le transistor bipolaire contrôle le déplacement de charges électriques à travers deux jonctions PN en opposition (transistors NPN ou PNP) [I.5], [I.6], alors que le transistor à effet de champ contrôle le déplacement de charges (électrons ou trous) entre source et drain au travers d'un canal par une troisième électrode, la grille [I.7], [I.8]. En régime de commutation, malgré une bonne robustesse aux fortes puissances, le transistor bipolaire présente plusieurs inconvénients comparativement au transistor à effet de champ, comme une consommation importante de la commande due au passage en continu d'un courant électrique, des temps de commutation plus élevés (de plusieurs centaines de nanosecondes comparé à quelques dizaines de nanosecondes maximum pour un transistor à effet de champ). Pour des applications de conversion d'énergie à hautes fréquences, on préfèrera donc la structure à effet de champ plus performante, notamment avec l'exploitation actuelle des matériaux « grands gap ». Parmi les structures de composant SiC et GaN les plus populaires pour des applications d'électronique de puissance, on citera les transistors « Metal Oxyde Semiconductor Field Effet Transistor » (MOSFET) en SiC [I.8] et « High Electron Mobility Transistor » (HEMT) en GaN.

Avec l'émergence des matériaux grands gap, des diodes de type Schottky combinant faible tension de seuil, recouvrement inverse quasi inexistant (faible charge stockée) sont aujourd'hui disponibles [I.7]. Ces composants s'ajoutent aux transistors MOSFET et HEMT sur la liste des semi-conducteurs les plus prometteurs dans l'optique de la montée en fréquence des convertisseurs statiques [I.9]. Une

Chapitre I : Introduction à la modélisation de transistors de puissance GaN pour la conception de convertisseurs statiques fonctionnant à hautes fréquences

présentation plus détaillée des diodes et transistors de puissance est proposée dans les paragraphes suivants.

#### I.1.1.2. La diode de puissance

Les semi-conducteurs présents dans les systèmes en électronique de puissance sont utilisés pour laisser passer ou interrompre le courant électrique périodiquement (fonctionnement en interrupteur). Ces composants possèdent deux états de fonctionnement en régime établi : un état passant (ON) et un état bloqué (OFF).

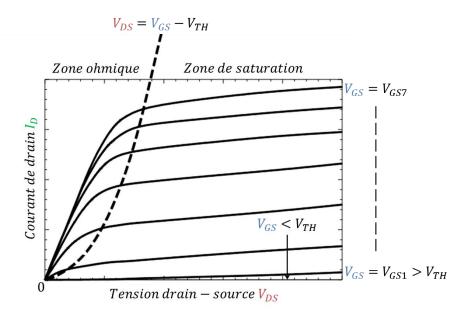

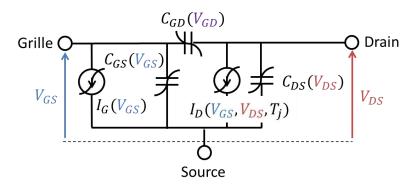

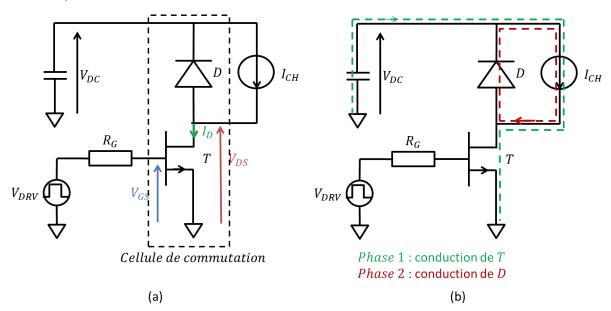

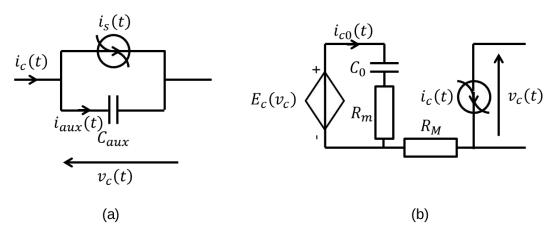

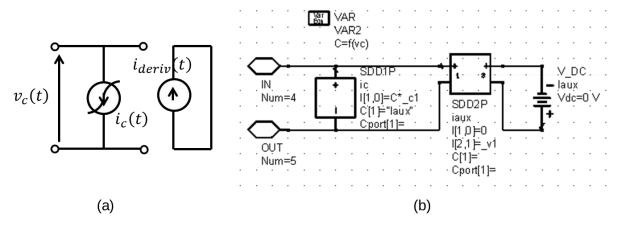

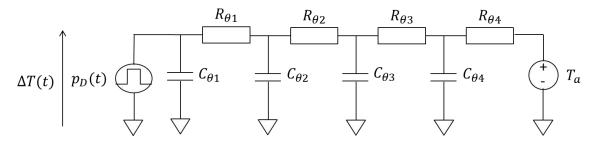

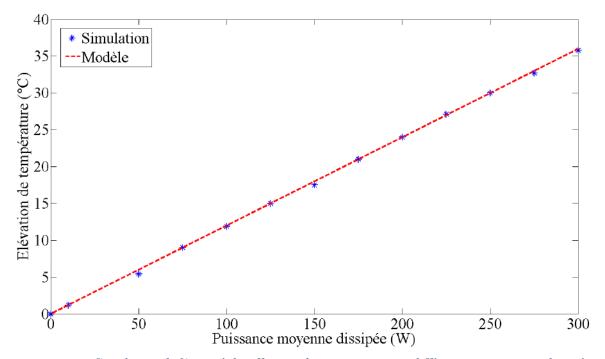

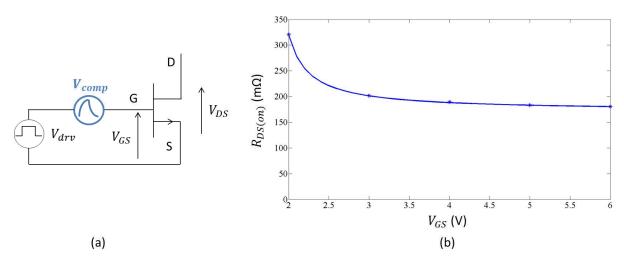

Il existe des semi-conducteurs non-commandés tels que les diodes. La diode est un dipôle formé soit par une association de deux semi-conducteurs de dopage opposé soit par une association métal/semi-conducteur, formant une jonction et deux terminaisons : une anode, notée A, et une cathode, notée K [I.5].